INSTITUT NATIONAL DE RECHERCHE EN INFORMATIQUE ET EN AUTOMATIQUE

## Projet EP-ATR

Environnement de programmation d'applications temps réel

## Rennes

## Table des matières

| 1 Composition de l'équipe |                               |                                                                               |                 |  |  |  |

|---------------------------|-------------------------------|-------------------------------------------------------------------------------|-----------------|--|--|--|

| <b>2</b>                  | Pré                           | Présentation et objectifs généraux                                            |                 |  |  |  |

|                           | 2.1                           | Contexte des études                                                           | 3               |  |  |  |

|                           | 2.2                           | Objectif général du projet                                                    | 4               |  |  |  |

|                           | 2.3                           | Conception synchrone                                                          | 5               |  |  |  |

|                           | 2.4                           | Thèmes de recherche                                                           | 6               |  |  |  |

|                           |                               | 2.4.1 Description d'applications                                              | 6               |  |  |  |

|                           |                               | 2.4.2 Étude des propriétés des processus synchrones                           | 7               |  |  |  |

|                           |                               | 2.4.3 Méthodes et outils pour la conception d'architectures de mise en œuvre  | 8               |  |  |  |

|                           |                               | 2.4.4 Développements et expérimentations                                      | 8               |  |  |  |

|                           | 2.5                           | Problèmes ouverts et perspectives                                             | 9               |  |  |  |

| 3                         | Fon                           | dements scientifiques                                                         | 10              |  |  |  |

| •                         | 3.1                           | Spécification et programmation synchrone                                      | 10              |  |  |  |

|                           | 0.1                           | 3.1.1 Sémantique synchrone                                                    |                 |  |  |  |

|                           |                               | 3.1.2 Langage Signal                                                          | 12              |  |  |  |

|                           | 3.2                           | Vérification et synthèse                                                      | 13              |  |  |  |

|                           | 0.2                           | vermeuten et by nenese                                                        | 10              |  |  |  |

| 4                         | Dor                           | naines d'applications                                                         | 17              |  |  |  |

|                           | 4.1                           | Panorama                                                                      | 17              |  |  |  |

|                           | 4.2                           | Télécommunications                                                            | 17              |  |  |  |

|                           | 4.3                           | Énergie                                                                       | 18              |  |  |  |

|                           | 4.4                           | Avionique                                                                     | 19              |  |  |  |

| 5                         | Log                           | iciels                                                                        | 20              |  |  |  |

|                           | 5.1                           | Environnement de programmation Polychrony pour Signal                         | 20              |  |  |  |

|                           | 5.2                           | Sigali                                                                        | 23              |  |  |  |

| 6                         | Ρáα                           | ultats nouveaux                                                               | 24              |  |  |  |

| U                         | 6.1                           | Évolutions de Signal et de son environnement                                  |                 |  |  |  |

|                           | 6.2                           | Sémantique des diagrammes d'état de UML                                       |                 |  |  |  |

|                           | 6.3                           | Objets synchrones                                                             | $\frac{20}{27}$ |  |  |  |

|                           | 6.4                           | Multi-formalisme et modélisation synchrone de la norme IEC 1131 de            | ۷ ۱             |  |  |  |

|                           | 0.4                           | programmation des systèmes de contrôle                                        | 28              |  |  |  |

|                           | 6.5                           | Vérification des programmes                                                   | 28              |  |  |  |

|                           | 6.6                           | Synthèse automatique de contrôleurs                                           | $\frac{20}{30}$ |  |  |  |

|                           | 6.7                           | Mises en œuvre distribuées et modélisation d'architectures de communication . | 33              |  |  |  |

|                           | 6.8                           | Modélisation de circuits et synthèse de matériel                              | 35              |  |  |  |

|                           | 6.9                           | Techniques d'algèbre MaxPlus pour l'évaluation de performances                | 36              |  |  |  |

|                           | $\mathbf{u} \cdot \mathbf{g}$ | rechinques a aigeore maxi lus pour revaluation de performances                | 50              |  |  |  |

| 7  | Contrats industriels (nationaux, européens et internationaux) |                                                                              |    |  |  |

|----|---------------------------------------------------------------|------------------------------------------------------------------------------|----|--|--|

|    | 7.1                                                           | Projet RNTL Expresso, convention n°2 01 C 0299 00 31307 01 1                 |    |  |  |

|    |                                                               | (06/2001 – 05/2003)                                                          | 37 |  |  |

|    | 7.2                                                           | Projet RNTL Acotris, convention n°2 00 C 0527 00 31307 01 1                  |    |  |  |

|    |                                                               | (02/2001 – 07/2003)                                                          | 38 |  |  |

|    | 7.3                                                           | Projet IST SafeAir, convention n°1 00 C 0149 00 31307 00 5 (01/2000-06/2002) | 39 |  |  |

|    | 7.4                                                           | Projet Castor, convention n°1 00 C 0156 00 31399 01 2 $(10/1999-04/2002)$    | 41 |  |  |

|    | 7.5                                                           | TNI                                                                          | 41 |  |  |

| 8  | Actions régionales, nationales et internationales             |                                                                              |    |  |  |

|    | 8.1                                                           | Actions internationales                                                      | 42 |  |  |

|    |                                                               | 8.1.1 Accueil de chercheurs étrangers                                        | 42 |  |  |

| 9  | Diff                                                          | fusion de résultats                                                          | 42 |  |  |

|    | 9.1                                                           | Animation de la communauté scientifique                                      | 42 |  |  |

|    | 9.2                                                           | Enseignement universitaire                                                   |    |  |  |

|    | 9.3                                                           | Participation à des colloques, séminaires, invitations                       | 42 |  |  |

| 10 | Bib                                                           | liographie                                                                   | 43 |  |  |

#### 1 Composition de l'équipe

#### Responsable scientifique

Paul Le Guernic [DR Inria]

## Assistante de projet

Huguette Béchu [TR Inria]

#### Personnel Inria

Albert Benveniste [DR, projet Sigma 2]

Patricia Bournai [IR, Atelier, à mi-temps dans le projet]

Thierry Gautier [CR]

Hervé Marchand [CR]

Luc-Michel Sévère [ingénieur associé, à partir du 1<sup>er</sup> octobre 2001]

Jean-Pierre Talpin [CR]

#### Personnel CNRS

Loïc Besnard [IR, Atelier]

#### Personnel Université de Rennes 1

Bernard Houssais [maître de conférences]

Sophie Pinchinat [maître de conférences, détachée en tant que CR Inria]

Christophe Wolinski [maître de conférences, jusqu'au 31 août 2001]

#### Chercheurs doctorants

Abdoulaye Elhadji Gamatié [bourse Inria]

Fernando Jiménez Fraustro [bourse du gouvernement mexicain, jusqu'au 31 mars 2001]

Mickaël Kerbœuf [bourse MENRT]

Sylvain Kerjean [bourse MENRT]

Pierre Le Maigat [bourse MENRT]

Mirabelle Nebut [bourse MENRT jusqu'au 31 août 2001, demi poste Ater à l'Université

de Rennes 1 à partir du 1<sup>er</sup> septembre 2001]

Stéphane Riedweg [bourse Inria-région]

Laurent Vibert [normalien]

Yunming Wang [bourse CIES, jusqu'au 31 mars 2001]

#### 2 Présentation et objectifs généraux

Mots clés: EP-ATR, système enfoui, temps réel, conception synchrone.

Le projet EP-ATR conduit des travaux à la fois théoriques, méthodologiques, algorithmiques et d'expérimentation sur le thème de la conception de systèmes (ou d'applications) enfouis temps réel; ces travaux sont basés sur une approche synchrone de la description de processus.

#### 2.1Contexte des études

Mots clés: système enfoui, système temps réel, système critique, certification, cycle en V, transformation de programme, conception conjointe, composants, vérification, méthode

formelle.

Les produits informatiques enfouis, le plus souvent avec des contraintes temps réel fortes, dans des systèmes industriels de grande envergure comme les centrales nucléaires, les systèmes de contrôle aérien, les télécommunications, ou dans des systèmes de taille plus modeste (avions, automobiles...), mais aussi de petite taille comme les processeurs ou contrôleurs divers utilisés dans des produits de grande diffusion, ont pour caractéristique commune de devoir fonctionner selon un mode de coopération permanente avec un environnement. Un système enfoui peut ainsi influencer sérieusement le comportement de cet environnement, non seulement par son activité mais aussi par son inactivité : ainsi le dysfonctionnement d'un système par exemple de commande de vol peut entraîner un accident d'avion; celui d'un système de régulation thermique, la perte d'une entreprise avicole, par exemple. En fonction de la gravité des conséquences prévisibles d'un dysfonctionnement du composant informatique sur les plans économique, humain, ou social, le développement des applications considérées est l'objet de procédures plus ou moins lourdes, telles que certification pour les systèmes critiques, visant à la réduction des risques d'erreurs ou de défaillances du système.

Traditionnellement le développement de ces applications s'appuie sur un cycle en V qui de l'amont vers l'aval, en partant d'un cahier des charges, passe par l'établissement de spécifications aussi complètes et consistantes que possible, sur lesquelles s'appuie la conception globale puis détaillée à partir de laquelle est produit le codage de l'application. Ce processus de conception s'appuye à des niveaux et à des degrés divers sur des techniques de transformation de programmes, sur des techniques de conception conjointe, sur l'utilisation de composants matériels ou logiciels. La confiance dans le produit réalisé repose sur le respect de procédures codifiées incluant un chemin de vérification, inverse du chemin de conception, allant du test unitaire au test système. Les méthodes formelles, s'appuyant sur des modèles mathématiques correctement définis, trouvent aujourd'hui une place grandissante dans ces méthodologies et sont d'ores et déjà admises, voire recommandées, comme complément dans les méthodes traditionnelles, y compris dans des documents normatifs.

### 2.2 Objectif général du projet

Mots clés: modèles théoriques, méthodologie de conception, prototypes logiciels, applications, traitement temps réel du signal, télécommunication, avionique, automobile, temps réel, programmation synchrone, génération de code enfoui, génération de code distribué, architecture hétérogène, circuits.

C'est dans ce cadre que s'inscrivent les activités conduites par le projet EP-ATR : elles visent à proposer des modèles théoriques, des enrichissements du contexte méthodologique traditionnel (cycle en V) prenant en compte ces modèles, et enfin des logiciels (à l'état de prototype avancé) permettant de mettre en œuvre ces méthodes de conception nouvelles et de conduire des expérimentations des solutions proposées. Ayant débuté dans le domaine du traitement temps réel du signal en télécommunication (avec le soutien du Cnet et de la DGA, nos travaux ont trouvé de nouveaux contextes d'applications, en particulier par des collaborations suivies avec différents projets de l'Inria (robotique, image), avec EDF, puis dans le domaine de l'avionique avec nos partenaires des projets Esprit Sacres, Syrf, puis IST Safeair, dans le domaine des

télécommunications, là encore en collaboration avec des projets de l'Inria, avec Alcatel et le Cnet, et dans le domaine de l'automobile, avec les industriels impliqués dans le projet AEE, et là aussi différents projets de l'Inria et d'autres partenaires universitaires.

En même temps que se sont élargis les domaines d'applications, les problèmes que nous considérons se sont étendus d'une part en amont vers la spécification de systèmes temps réel, d'autre part en aval vers la génération de code enfoui, éventuellement sous la forme de code distribué sur des architectures hétérogènes et au delà, vers la prise en compte de composants matériels, en synthèse et en modélisation.

Ces travaux, qui concernent ainsi aujourd'hui le développement des applications temps réel depuis leur spécification jusqu'à leur mise en œuvre matérielle, reposent sur une modélisation homogène des niveaux de description rencontrés au cours de la conception : cette approche, fondée sur un modèle mathématique de la *programmation synchrone*, permet de mettre formellement en relation différentes versions de l'application, réduisant en cela les risques liés à des ruptures dans le cycle de leur conception.

## 2.3 Conception synchrone

$\textbf{Mots clés}: \ conception \ synchrone, \ Signal, \ contraintes, \ non-déterminisme, \ système \ réactif.$

L'idée assez simple du modèle de conception synchrone est de considérer qu'un programme plongé dans un environnement (constitué de procédés, d'opérateurs, d'autres programmes), interagit significativement avec cet environnement au travers d'un ensemble fini de supports de communication à des instants formant un ensemble dénombrable partiellement ordonné. À chaque instant, plusieurs actions (messages reçus, émis, calculs...) peuvent être effectuées ; elles sont alors simultanées et possèdent un même indice temporel. L'écoulement du temps résulte des successions de ces communications, mais aussi de changements explicites décrits dans l'algorithme que le programme met en œuvre (par exemple pour une équation  $y_t = f(x_{t-1})$ , la sortie y sera simultanée à chaque occurrence suivante de l'entrée x). Selon les formalismes, les sorties calculées sont, sauf changement explicite dans le programme, soit simultanées aux entrées qui ont provoqué leur calcul comme dans les langages Esterel, Lustre ou Signal, soit produites à l'instant suivant comme dans Statemate ou VHDL par exemple.

Le langage Signal [8], conçu et mis en œuvre dans le projet, est de plus, comme Lustre, construit selon une approche flot de données faisant d'un programme un système d'équations. À la différence de ce qui se passe en Lustre, le système d'équations d'un programme Signal décrit par une relation des contraintes entre les signaux d'entrée et de sortie du système; ceci permet d'utiliser Signal pour donner des spécifications partielles ou décrire des comportements non déterministes. Cette banalisation (néanmoins partielle) des entrées et des sorties permet en outre la spécification et la programmation de systèmes réactifs [HP85] mais aussi «pro-actifs» (pouvant par exemple contraindre leurs entrées).

<sup>[</sup>HP85] D. HAREL, A. PNUELI, « On the development of reactive systems », in: Logics and models of concurrent systems, K. Apt (éditeur), NATO Advanced Study Institute on Logics and Models for Verification of Concurrent Systems, Springer Verlag, p. 477–498, New-York, 1985.

#### 2.4 Thèmes de recherche

Mots clés: Signal, conception synchrone, vérification, transformation de programme, communication synchrone/asynchrone, architecture hétérogène, composant matériel, format commun, programmation synchrone, DC+, Statecharts, automatismes industriels, système dynamique polynomial, synthèse de contrôleur, BDD.

S'appuyant sur une expression en Signal des différentes versions d'un système en cours de conception, la méthodologie que nous développons consiste en l'application d'une série de transformations de descriptions respectant le schéma suivant :

- spécification, conception et vérification de l'application indépendamment de l'architecture cible, grâce à l'hypothèse de synchronisme et au non-déterminisme qui permet d'une part de fournir un modèle du comportement de l'environnement, d'autre part de donner des spécifications partielles;

- affinement progressif vers l'implémentation (conception détaillée incluant le partitionnement) guidé par des simulations/vérifications à différents niveaux; à cette étape, la cible est une architecture logicielle pouvant être vérifiée et évaluée; cette cible peut comporter des spécifications de composants prédéfinis;

- implantation effective du schéma d'exécution obtenu sur des architectures y compris asynchrones et distribuées, en relâchant au besoin l'hypothèse de synchronisme (tout en restant dans le cadre du modèle synchrone), et en garantissant une implémentation correcte;

- génération de code exécutable, de descriptions de composants matériels ou de composants hybrides matériels/logiciels.

Nos activités de recherche concernent les différentes étapes de ce schéma de conception. Comme certaines de ces activités concernent plusieurs de ces étapes, nous distinguons ici, pour une meilleure lisibilité, les thèmes suivants : description d'applications, étude des propriétés des processus synchrones, méthodes et outils pour la conception d'architectures de mise en œuvre, développements et expérimentations.

#### 2.4.1 Description d'applications

La description d'une application, tant au niveau de la spécification que de la conception, suppose l'existence d'un langage suffisamment expressif pour les classes d'applications visées; la réduction des ruptures dans le cycle de conception est favorisée par le support logiciel des traitements dans une sémantique homogène. Les études portant sur l'augmentation du pouvoir d'expression du langage Signal ont pour but d'étendre le domaine d'application des techniques synchrones, soit par la définition de relations sémantiques entre les formalismes synchrones et d'autres formalismes, soit par l'adjonction de nouvelles primitives ou de nouveaux concepts dans le langage lui-même.

– Avec la société TNI (voir section 7.5) qui commercialise Sildex, un environnement de programmation fondé sur Signal, nous avons travaillé à la définition d'une nouvelle version (V4) dont l'une des principales extensions porte sur la modularité; d'autres extensions ont également été définies et de nouvelles techniques de compilation sont implémentées (voir section 6.1);

- Entreprises initialement dans le cadre d'un ancien projet avec les Laboratoires de Marcoussis, les études sur les liens entre le paradigme objet et le modèle synchrone trouvent un nouvel élan dans les travaux auxquels nous participons sur la conception de BDL et le lien avec UML; BDL est un formalisme reposant sur le modèle synchrone pour la spécification de comportements d'objets (voir section 6.2). Nous travaillons d'autre part à l'unification des paradigmes synchrone et objet dans un même cadre formel (voir section 6.3).

Le format commun de la programmation synchrone (DC+) résulte de travaux menés depuis plusieurs années, tout d'abord par les équipes françaises dans lesquelles ont été conçus les langages synchrones Esterel, Lustre et Signal au sein du groupement C2A, puis dans le cadre d'un projet européen Eureka (Synchron), et enfin dans le cadre des projets européens LTR Syrf et R&D Sacres [Sac97]. La définition de ce format a été décidée en vue de favoriser le partage de logiciels issus de la communauté synchrone, mais aussi de permettre une large ouverture vers d'autres formalismes en amont, et d'autres outils, latéralement et en aval. Il est aujourd'hui intégré à l'environnement Signal (voir section 5.1).

Le projet européen Sacres a eu précisément pour objectif de développer un environnement de conception multi-formalisme synchrone à destination des applications critiques enfouies. Il se poursuit aujourd'hui sous une autre forme dans le cadre du projet européen IST SafeAir (voir section 7.3). Une autre étude basée sur le multi-formalisme concerne la modélisation et traduction des langages de programmation d'automatismes industriels de la norme IEC 1131 (voir section 6.4).

#### 2.4.2 Étude des propriétés des processus synchrones

Un programme Signal décrit le comportement d'un système de transitions dont divers formalismes permettent d'étudier les propriétés.

Jusqu'à une période récente, nos travaux sur ce thème ont porté essentiellement sur une modélisation des comportements par des systèmes dynamiques polynomiaux sur les entiers modulo 3 (permettant le codage des booléens et de l'absence d'occurrence d'un signal à un instant donné). Un système de calcul symbolique (Sigali) a été développé dans ce cadre (voir section 5.2). C'est dans ce système que sont maintenant étudiées des techniques de synthèse de contrôleurs, techniques utilisables pour affiner des spécifications, pour aider à la conduite de postes de commandes, voire à la génération automatique de tests (voir section 6.6).

Les systèmes dynamiques permettent d'analyser (partiellement) les trajectoires des processus dans un ensemble d'états résultant de la combinaison de variables du programme Signal. Cet ensemble lui-même est l'objet, dès la compilation, de calculs qui reposent sur une représentation par hiérarchie de BDD (Binary Decision Diagrams — représentation de formules booléennes) : ceci est appelé calcul d'horloges [1]. Ces calculs sont utilisés en particulier pour effectuer des transformations de programmes en vue de vérification, de distribution et de génération de code.

Des approches complémentaires pour la vérification de propriétés sont fournies par les techniques d'interprétation abstraite, permettant la prise en compte de signaux numériques,

par exemple (voir section 6.5).

## 2.4.3 Méthodes et outils pour la conception d'architectures de mise en œuvre

La définition de l'architecture supportant l'application temps réel peut comporter différentes classes de composants comme des processeurs standards, des DSP, des Asics, etc., et c'est donc dans la perspective de mise en œuvre sur de telles cibles hétérogènes que nous inscrivons aussi bien nos études sur la conception détaillée et le codage que des activités relevant de la conception conjointe matériel/logiciel.

Le problème du partitionnement d'un programme flot de données synchrone est abordé en s'attachant aux propriétés structurelles du graphe de l'application; supposant donnée une répartition du code sur une architecture cible (cette répartition peut résulter d'algorithmes d'optimisation ou être explicitée comme spécification non fonctionnelle, par exemple pour des raisons de traçabilité), nous nous proposons de produire, par des transformations locales à chaque composant de cette architecture, à la fois le code pour ces composants et les protocoles de communication à mettre en œuvre (voir section 6.7). Cette mise en œuvre peut être «Globalement Asynchrone Localement Synchrone» (Gals). Le cadre théorique de nos recherches permet de caractériser des mises en œuvre synchrones ou partiellement désynchronisées en terme de préservations de propriétés de flots, d'ordres partiels, de taille mémoire, par rapport au programme initial.

Pour la génération de composants matériels ou de code exécutable sur un processeur programmable, l'approche que nous adoptons est là encore celle de la transformation de programmes conduisant à une expression en Signal aussi proche que possible de la structure du code cible (C ou VHDL actuellement). Cette approche diminue les risques d'incorrection liés au passage à un autre langage.

Elle est accompagnée d'études sur la modélisation synchrone de composants matériels en vue du prototypage rapide de circuits spécifiques, qui participent à l'activité grandissante du projet sur le thème de la conception conjointe matériel/logiciel (voir section 6.8).

Dans l'approche synchrone, les durées d'exécution ne sont pas directement prises en compte. La prise en compte de ces durées, nécessaire à la vérification de la correction de la mise en œuvre en regard des contraintes temps réel, est effectuée en considérant une interprétation qui, à un programme synchrone et une architecture donnée, associe un programme synchrone sur nombres entiers; l'image du programme initial modélise les durées d'exécution de la mise en œuvre. On peut alors simuler le programme image (voir section 6.1) ou chercher à utiliser des techniques analytiques, comme par exemple celles qu'offre l'algèbre MaxPlus (voir section 6.9).

#### 2.4.4 Développements et expérimentations

Les travaux théoriques conduits dans le projet aboutissent à des prototypes mettant en œuvre les algorithmes conçus au cours de ces études. Nous nous efforçons de conserver et diffuser ce savoir-faire du projet par une intégration dans un environnement de conception construit autour du langage Signal. Une section est consacrée à la présentation de ce logiciel (section 5.1).

Des expérimentations sont conduites pour valider les algorithmes en relation avec des industriels. Elles concernent également la diffusion des principes synchrones par des développements donnant à des formalismes divers une traduction en Signal. Enfin l'étude d'applications en coopération avec des industriels ou des projets académiques est une source importante des problèmes nouveaux que traite le projet EP-ATR.

## 2.5 Problèmes ouverts et perspectives

Mots clés: système hybride, génération de test.

Le développement d'un système enfoui temps réel, tel que décrit dans ces pages, prend des processus discrets pour modèles des procédés physiques de l'environnement et suppose donc l'étude algorithmique (par exemple de lois de commande) effectuée. Or la validation d'un système complet doit prendre en compte, soit par modèle, soit dans des maquettes matérielles (et souvent les deux), les fonctions continues dirigeant le comportement des procédés. Si des travaux d'interfaçage entre des langages synchrones et des outils dédiés au continu tels que Matlab et Simulink ont été entrepris, il reste beaucoup à faire pour obtenir une réelle intégration des formalismes discrets et continus dans des systèmes hybrides.

Un obstacle sérieux à la mise en œuvre correcte par construction des systèmes temps réel reste le lien entre temps physique et temps logique et entre différents grains de temps discret, en particulier pour les points suivants :

- Prise en compte des événements fournis par l'environnement le plus souvent asynchrone au programme synchrone : les études sur les modèles de communication synchrone/asynchrone sont à compléter.

- Si nous savons définir correctement des procédures de raffinement efficaces portant sur l'espace (adjonction/suppression de variables), en ce qui concerne le temps, les études que nous avons entreprises tant par le biais des transformations affines, que dans les cadres du (re)timing monocadencé ou de l'utilisation de l'algèbre MaxPlus, restent encore de portée trop limitée pour satisfaire les besoins de transformation visant à éliminer les systèmes d'exploitation dans les systèmes critiques enfouis.

Pour aller vers la vérification complète des propriétés d'un système, il est nécessaire de prendre en compte des domaines plus riches que les booléens. Nous menons des études en ce sens visant à compléter dans un premier temps le calcul d'horloges par des techniques provenant des résolutions de contraintes sur domaines finis; pour aller plus loin, il deviendra nécessaire d'adapter des techniques de démonstration automatique.

Même si les techniques formelles progressent, tant dans les esprits de leurs utilisateurs potentiels que dans les performances des algorithmes mis en œuvre, la simulation et le test resteront des activités nécessaires à la validation d'un système. C'est pourquoi nous envisageons de participer à des études sur la génération automatique de tests, principalement d'intégration, qui posent des problèmes non résolus. Ces études pourront se faire en corrélation étroite avec les méthodes de synthèse automatique de contrôleurs actuellement développées dans le projet.

En supposant un système correct vis-à-vis de spécifications de comportements nominaux, l'étude du comportement du système en présence de défaillances reste un sujet majeur pour les entreprises mettant en œuvre des systèmes critiques. Les études théoriques (qui bien sûr ne

peuvent concerner les seuls informaticiens) doivent être développées.

Ces activités et d'autres thèmes de recherche connexes seront poursuivis dans les nouveaux projets de recherche issus du renouvellement des projets du thème 1c à l'Irisa. Si le projet EP-ATR s'est arrêté en effet courant 2001, la plupart des membres du projet se retrouvent dans les nouveaux projets suivants :

- projet Espresso : P. Le Guernic, Th. Gautier, L.-M. Sévère, J.-P. Talpin, L. Besnard,

B. Houssais, A. Gamatié, M. Kerbœuf, S. Kerjean, M. Nebut, L. Vibert;

- projet S4: A. Benveniste, S. Pinchinat, S. Riedweg;

- projet VerTeCs : H. Marchand.

Le projet Espresso notamment, sous la responsabilité de J.-P. Talpin, assurera le développement et la diffusion de la plateforme Polychrony développée autour de Signal.

## 3 Fondements scientifiques

## 3.1 Spécification et programmation synchrone

Mots clés : conception synchrone, sémantique synchrone, programmation synchrone, Signal, transformation de programme.

Résumé: Nous définissons la sémantique fonctionnelle d'un programme synchrone comme un ensemble de suites de valuations des variables de ce programme dans un domaine de valeurs complété par une représentation de l'absence d'occurrence d'une variable. Les opérateurs du langage Signal décrivent des relations sur de telles suites. Le compilateur de Signal est un outil formel capable de synthétiser la synchronisation globale d'un programme et l'ordonnancement de ses calculs. De nombreuses phases de compilation s'expriment par des transformations de programmes définies par des homomorphismes de programmes Signal.

Les usages différents des termes *synchrone* et *asynchrone* selon les contextes dans lesquels ils apparaissent font qu'il nous semble nécessaire de préciser, autant que possible, ce qui constitue l'essence même du paradigme synchrone [BB91,BCLH93,Ber89,Hal93]. Les points suivants apparaissent comme caractéristiques de l'approche synchrone :

- Le comportement des programmes synchrones progresse via une suite infinie d'actions composées.

- Chaque a2ction composée est constituée d'un nombre borné d'actions élémentaires, pour les langages Esterel, Lustre et Signal.

- [BB91] A. Benveniste, G. Berry, « The Synchronous Approach to Reactive and Real-Time Systems », Proceedings of the IEEE 79, 9, Septembre 1991, p. 1270–1282.

- [BCLH93] A. Benveniste, P. Caspi, P. Le Guernic, N. Halbwachs, « Data-Flow Synchronous Languages », in: Lecture Notes in Computer Science 803, Proc. of the REX School/Symposium, Noordwijkerhout, Netherlands, J. W. de Bakker, W. de Roever, G. Rozenberg (éditeurs), 803, Springer-Verlag, p. 1-45, Juin 1993.

- [Ber89] G. Berry, « Real-Time Programming: special purpose or general purpose languages », in: Information processing 89, G. X. Ritter (éditeur), Elsevier Science Publisher B.V., 1989.

- [Hal93] N. Halbwachs, Synchronous programming of reactive systems, Kluwer, 1993.

- À l'intérieur d'une action composée, les décisions peuvent être prises sur la base de l'absence de certains événements, comme il apparaît sur l'exemple des trois instructions suivantes, issues respectivement de Esterel, Lustre, et Signal :

present x else 'stat' l'action stat est exécutée en l'absence du signal x.

y = current x

en l'absence d'occurrence du signal x,

y prend la valeur de la dernière occurrence de x.

y := x default z

en l'absence d'occurrence des signaux x et z,

y est absent,

sinon en l'absence d'occurrence du signal x,

y prend la valeur de z.

- Lorsqu'elle est définie, la composition parallèle de deux programmes s'exprime toujours par la composition des couples d'actions composées qui leur sont respectivement associées, elle-même obtenue par la conjonction de leurs actions élémentaires respectives.

Pour ce qui concerne la spécification de programmes (ou de propriétés), la règle ci-dessus est clairement la bonne définition de la composition parallèle.

S'il s'agit également de programmation, la nécessité que cette définition soit compatible avec une sémantique opérationnelle complique largement la condition «lorsqu'elle est définie».

#### 3.1.1 Sémantique synchrone

La sémantique fonctionnelle d'un programme Signal est décrite comme l'ensemble des suites admissibles de valuations des variables de ce programme dans un domaine de valeurs complété par la notation d'absence d'occurrence [4, 9].

Considérant :

- A, un ensemble de variables,

- D, un domaine de valeurs incluant les booléens,

- $-\perp$ , n'appartenant pas à D,

une trace T sur  $A_1 \subset A$  est une fonction  $T: \mathbb{N} \to A_1 \to (D \cup \{\bot\})$ .

Pour tout  $k \in \mathbb{N}$ , un événement sur  $A_1$  est une valuation T(k): une trace est une suite d'événements. On appelle événement nul l'événement dans lequel chaque valeur est égale à  $\perp$ .

Pour toute trace T, il existe une trace F unique appelée flot, notée flot(T), dont la soussuite des événements non nuls est égale à celle de T et initiale dans F. La projection  $\pi_{A_2}(F)$ sur un sous-ensemble  $A_2 \subset A_1$  d'un flot F, défini sur  $A_1$ , est le flot flot(T) pour T trace des restrictions des événements de F à  $A_2$ .

Un processus P sur  $A_1$  est alors défini comme un ensemble de flots sur  $A_1$ . L'union de l'ensemble des processus sur  $A_i \subset A$  est noté  $\mathcal{P}_A$ .

Étant donné  $P_1$  et  $P_2$  deux processus définis respectivement sur des ensembles de variables  $A_1$  et  $A_2$ , leur composition, notée  $P_1|P_2$ , est l'ensemble des flots F définis sur  $A_1 \cup A_2$  tels que  $\pi_{A_1}(F) \in P_1$  et  $\pi_{A_2}(F) \in P_2$ . La composition de deux processus  $P_1$  et  $P_2$  est ainsi définie par l'ensemble de tous les flots respectant, en particulier sur les variables communes, l'ensemble des contraintes imposées respectivement par  $P_1$  et  $P_2$ .

Soit  $\mathbf{1}_{\mathcal{P}}$  le processus ayant comme seul élément la trace (unique) sur l'ensemble vide de

variables. On montre alors que  $(\mathcal{P}_A, \mathbf{1}_{\mathcal{P}}, |)$  est un monoïde commutatif (cette propriété rend possibles les transformations de programmes mentionnées en 3.1.2):

$$(P_1|P_2)|P_3 = P_1|(P_2|P_3)$$

$P_1|P_2 = P_2|P_1$

$P|\mathbf{1}_{\mathcal{P}} = P$

De plus, pour tout  $A_1 \subset A$ , les processus  $\mathbf{0}_{\mathcal{P}}$  définis par l'ensemble vide de flots sur  $A_1$  sont absorbants :

$$P|\mathbf{0}_{\mathcal{P}}=\mathbf{0}_{\mathcal{P}}$$

Enfin, l'opérateur de composition est idempotent (ceci autorise la réplication de processus) :

$$P|P = P$$

Par ailleurs, si P est un processus sur  $A_1$  et Q un processus sur  $A_2$  inclus dans  $A_1$ , on a :

$$P|Q = P$$

si et seulement si tout flot de la projection de P sur  $A_2$  est un flot de Q (Q est moins contraint que P).

### 3.1.2 Langage Signal

Un programme Signal [8] spécifie un système temps réel au moyen d'un système d'équations dynamiques sur des signaux. Les systèmes d'équations peuvent être organisés de manière hiérarchique en sous-systèmes (ou processus). Un signal est une suite de valeurs à laquelle est associée une horloge, qui définit l'ensemble discret des instants auxquels ces valeurs sont présentes (différentes de  $\bot$ ). Les horloges ne sont pas nécessairement reliées entre elles par des fréquences d'échantillonnage fixes : elles peuvent avoir des occurrences dépendant de données locales ou d'événements externes (comme des interruptions, par exemple).

Le langage Signal est construit sur un petit nombre de primitives, dont la sémantique est donnée en termes de processus tels que décrits ci-dessus. Les autres opérateurs de Signal sont définis en terme de ces primitives, et le langage complet fournit les constructions adéquates pour une programmation modulaire.

Pour un flot F, une variable X et un entier t on note, lorsqu'il n'y a pas de confusion possible,  $X_t$  la valeur F(t)(X) portée par X en t dans le flot F. On note par le même symbole une variable ou une fonction dans les domaines syntaxique et sémantique. Dans le tableau ci-dessous, on omet les événements nuls (qui, rappelons-le, terminent les flots ayant un nombre fini d'événements non nuls).

Le noyau de Signal se compose des primitives suivantes :

- Fonctions ou relations étendues aux suites :

$$\mathbf{Y} := \mathbf{f}(\mathbf{X}\mathbf{1}, \dots, \mathbf{X}\mathbf{n}) : \left\{ \begin{array}{l} \forall k, \mathbf{Y}_k = \ \bot \ \Rightarrow \ \mathbf{X}\mathbf{1}_k = \dots = \mathbf{X}\mathbf{n}_k = \bot \\ \forall k, \mathbf{Y}_k \neq \ \bot \ \Rightarrow \ \mathbf{Y}_k = \mathbf{f}(\mathbf{X}\mathbf{1}_k, \dots, \mathbf{X}\mathbf{n}_k) \end{array} \right.$$

- Retard (registre à décalage) :

$$\mathbf{Y} \; := \; \mathbf{X} \; \$ \mathbf{1} \; \text{init vO} \; : \left\{ \begin{array}{l} \forall k, \mathbf{Y}_k = \; \bot \; \Rightarrow \; \mathbf{X}_k = \bot \\ \mathbf{Y}_0 \neq \; \bot \; \Rightarrow \; \mathbf{Y}_0 = \mathtt{vO} \\ \forall k > 0, \mathbf{Y}_k \neq \; \bot \; \Rightarrow \; \mathbf{Y}_k = \mathbf{X}_{k-1} \end{array} \right.$$

- Extraction sur condition booléenne :

$$\mathbf{Y} := \mathbf{X} \text{ when } \mathbf{B} : \forall k, \left\{ \begin{array}{l} \mathbf{B}_k \neq true \ \Rightarrow \ \mathbf{Y}_k = \bot \\ \mathbf{B}_k = true \ \Rightarrow \ \mathbf{Y}_k = \mathbf{X}_k \end{array} \right.$$

Mélange avec priorité :

$$\texttt{Y} \; := \; \texttt{U} \; \texttt{default} \; \; \texttt{V} \; : \; \forall k, \left\{ \begin{array}{l} \texttt{U}_k \; \neq \; \bot \; \Rightarrow \; \texttt{Y}_k = \texttt{U}_k \\ \texttt{U}_k \; = \bot \; \Rightarrow \; \texttt{Y}_k = \texttt{V}_k \end{array} \right.$$

La composition de deux processus P|Q se traduit directement en la composition des ensembles de flots associés à chacun d'eux.

La restriction de visibilité de X, P / X est la projection de l'ensemble des flots associés à P sur l'ensemble des variables obtenu en enlevant X à celles de P.

Comme on peut le voir pour les primitives, chaque signal a sa propre référence temporelle (son «horloge», ou ensemble des instants où il est différent de  $\bot$ ). Par exemple, les deux premières primitives sont monocadencées : elles imposent que tous les signaux impliqués aient la même horloge. En revanche, dans la troisième et la quatrième primitives, les différents signaux peuvent avoir des horloges différentes. L'horloge d'un programme Signal est alors la borne supérieure de toutes les horloges des différents signaux du programme (les instants du programme sont les instants de l'un au moins de ces signaux).

Le compilateur de Signal consiste principalement en un système formel capable de raisonner sur les horloges des signaux, la logique, et les graphes de dépendance. En particulier, le calcul d'horloges [1] et le calcul de dépendances fournissent une synthèse de la synchronisation globale du programme à partir de la spécification des synchronisations locales (qui sont données par les équations Signal), ainsi qu'une synthèse de l'ordonnancement global des calculs spécifiés. Des contradictions et des inconsistances peuvent être détectées au cours de ces calculs.

On peut toujours ramener un programme P comportant des variables locales à un programme, égal à P, de la forme Q/A1/.../An où Q est une composition de processus élémentaires sans restriction de visibilité (i.e., sans R/A). Un principe général de transformation de programmes que nous appliquons (dans un but de vérification, pour aller vers la mise en œuvre, pour calculer des abstractions de comportement) est alors de définir des homomorphismes  $\mathcal{T}_i$  sur les programmes Signal, tels que Q est égal à la composition de ses transformés par  $\mathcal{T}_i$ . Grâce aux propriétés du monoïde commutatif, la transformation qui à Q associe cette composition est elle-même un homorphisme. On sépare ainsi un programme en différentes parties sur lesquelles seront alors appliqués des traitements spécifiques.

#### 3.2 Vérification et synthèse

Mots clés: Signal, transformation de programme, système dynamique polynomial,

vérification, synthèse de contrôleur, BDD.

Résumé: Le principe de transformation des programmes Signal permet de décomposer un programme en une partie décrivant le contrôle booléen et une partie contenant les calculs. Le contrôle lui-même définit un système dynamique qui peut être étudié sous plusieurs aspects à des fins de vérification et de synthèse : étude de l'ensemble des états admissibles (partie statique), pour laquelle une forme canonique arborescente utilisant des BDD a été définie; calcul dynamique s'appuyant sur la représentation équationnelle d'un automate.

En appliquant le principe de transformation, on décompose un programme P en une partie Q(P) contenant le contrôle booléen et une partie C(P) contenant les calculs non booléens, telles que P = Q(P)|C(P).

Toute propriété de sûreté, qui peut s'exprimer sous la forme d'un programme Signal R, satisfaite par Q(P), ce qui s'exprime sous la forme R|Q(P)=Q(P), est également satisfaite par P, puisqu'il résulte de P=Q(P)|C(P) que P=Q(P)|P (voir 3.1.1).

À une équation purement booléenne I correspond Q(I) = I; C(I) est alors l'élément neutre du monoïde.

D'une équation monocadencée, est extraite par Q la partie synchronisation des signaux ; on obtient par exemple pour x := y+z l'expression :

```

x ^= y ^= z | x := y+z

```

(x ^= y ^= z spécifie l'égalité des horloges de x, y et z).

Une équation de la forme x := y when b, dans laquelle x est non booléen, est décomposée en :  $x = (y \text{ when } b) \mid x := y \text{ when } b$ .

Une équation de la forme x := y default z, dans laquelle x est non booléen, est décomposée en :  $x ^= (y \text{ default } z) \mid x := y \text{ default } z$ .

Cette interprétation permet donc d'extraire, de façon automatique, par Q(P), l'aspect système à événements discrets, du système hybride spécifié par le programme. En raison de l'opérateur de retard qui introduit des indices temporels différents, le système est dynamique.

L'étude de ces systèmes dynamiques repose sur l'utilisation de techniques algébriques sur les corps de Galois. Elle vise à exprimer les propriétés des systèmes dynamiques et à donner une solution algorithmique pour leur vérification et pour la synthèse de systèmes satisfaisant certaines spécifications.

Q(P) est défini sur trois valeurs : { vrai, faux, absent }. La sémantique des opérateurs de Signal et l'approche flot de données équationnelle conduisent naturellement à un codage de Q(P) en équations polynomiales sur le corps  $\mathbf{Z}/3\mathbf{Z}$  (ou  $\mathcal{F}_3$ ), vrai, faux, absent étant représentés respectivement par 1, -1, 0 (+ est l'addition modulo 3,  $\times$  est la multiplication usuelle).

L'étude de la sémantique abstraite d'un programme Signal se ramène alors à l'étude des systèmes dynamiques de la forme :

$$\begin{cases} X_{n+1} &= P(X_n, Y_n) \\ Q(X_n, Y_n) &= 0 \\ Q_0(X_0) &= 0 \end{cases}$$

où X est un vecteur d'état dans  $(\mathbf{Z}/3\mathbf{Z})^n$  et Y un vecteur d'événements (interprétations abstraites de signaux) qui font évoluer le système.

Un tel système dynamique n'est qu'une forme particulière de système de transitions à espace d'états finis. C'est donc un modèle de système à événements discrets sur lequel il est possible de vérifier des propriétés [2] ou bien de faire du contrôle.

L'étude d'un programme consiste alors en :

- l'étude de sa partie statique, c'est-à-dire l'ensemble de contraintes

$$Q(X_n, Y_n) = 0$$

- l'étude de sa partie dynamique, c'est-à-dire le système de transitions

$$X_{n+1} = P(X_n, Y_n)$$

$$Q_0(X_0) = 0$$

et l'ensemble de ses états atteignables, etc.

Différentes techniques ont été développées pour ces deux problèmes. Les contraintes statiques sont essentielles pour la compilation des programmes Signal, et des techniques très efficaces ont été développées pour cela. La partie dynamique demande plus de calculs, et est utilisée principalement pour la vérification de propriétés; une technique plus générale — mais en retour moins efficace — a été développée pour la prendre en compte.

Le calcul d'horloges statique est au cœur du compilateur Signal; il en détermine largement ses performances. Ce calcul s'appuie sur l'ordre partiel des horloges, qui correspond à l'inclusion des ensembles d'instants (une horloge pouvant être plus fréquente qu'une autre).

La situation suivante doit être considérée :  $\mathbb{H}$  est l'horloge d'un signal, par exemple un signal à valeurs réelles  $\mathbb{X}$ , et  $\mathbb{K}$  est l'ensemble des instants où le signal  $\mathbb{X}$  dépasse un seuil :  $\mathbb{K}$  := when ( $\mathbb{X} > \mathbb{X}_MAX$ ). Alors 1/ chaque instant de  $\mathbb{K}$  est un instant de  $\mathbb{H}$ , et 2/ pour calculer le statut de  $\mathbb{K}$ , il faut d'abord connaître le statut de  $\mathbb{H}$ . Il y a donc à la fois le fait que  $\mathbb{K}$  est moins fréquent que  $\mathbb{H}$  et qu'il existe une contrainte de causalité de  $\mathbb{H}$  vers  $\mathbb{K}$ . Ceci est dénoté par  $\mathbb{H} \to \mathbb{K}$ . De tels sous-échantillonnages successifs organisent les horloges en plusieurs arbres, l'ensemble de ces arbres constituent la forêt d'horloges du programme considéré. Si un seul arbre est obtenu, la synchronisation du programme et son exécution s'en déduisent aisément.

La forêt associée à un programme donné n'est pas unique, la question de l'équivalence de forêts d'horloges se pose donc. Une forme canonique de forêt a été définie [1]. Un algorithme efficace pour trouver cette forme canonique a été développé. Il repose sur des manipulations préservant l'équivalence, prenant en compte l'ordre des variables résultant de la causalité, et combinées à des techniques BDD (Binary Decision Diagrams introduits par Bryant en 1986 [Bry86]).

Le calcul dynamique s'appuie sur la représentation équationnelle d'un automate : les automates, leurs états, événements et trajectoires sont manipulés au travers des équations qui les représentent. Calculer des trajectoires d'états ou d'événements, des états atteignables, des projections de trajectoires, des états de deadlock, etc., s'effectue alors sur les coefficients des équations polynomiales. De manière similaire, des techniques de synthèse de contrôle ont été

développées pour un système dynamique donné pour différents types d'objectifs de contrôle proposés par Manna et Pnueli [MP92,MP95], mais aussi pour des objectifs de contrôle portant sur la qualité de service.

La manipulation d'équations dans  $\mathcal{F}_3$  est tout à fait similaire à la manipulation d'équations booléennes. Une variante de la technique BDD, appelée TDD (Ternary Decision Diagrams — les nœuds ont trois valeurs possibles), a été développée pour réaliser ces calculs. Des expériences ont montré que le système formel Sigali qui en résulte peut effectuer en un temps raisonnable des preuves (ou de la synthèse de contrôleurs) sur des automates comportant plusieurs millions d'états atteignables.

#### Synthèse d'automatismes discrets

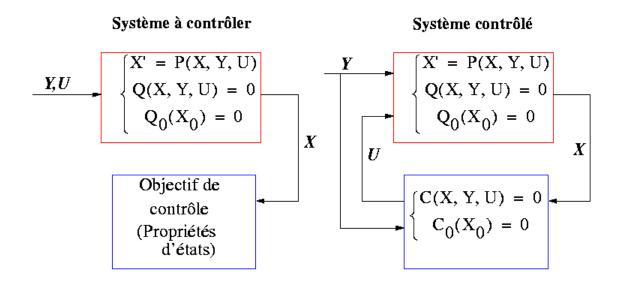

Partant d'un modèle global du système, contrôler un système dynamique polynomial consiste à se donner un objectif de commande (propriétés des trajectoires) et à synthétiser un contrôleur répondant à cet objectif [10]. Dans notre approche, le contrôleur synthétisé est une équation

Fig. 1 – Principe du contrôle

polynomiale, C(X,Y,U), dépendant de l'état courant du système, X, des événements incontrôlables, Y, et des commandes, U (figure 1). Le rôle de cette équation, ajoutée au système initial, consiste à forcer la valeur de ceux-ci en restreignant, pour un état donné, le choix possible des valeurs des commandes admissibles. Les événements contrôlables peuvent alors être vus comme des événements de sortie du contrôleur (respectivement des événements d'entrée du système initial).

<sup>[</sup>MP92] Z. Manna, A. Pnueli, The Temporal Logic of Reactive and Concurrent Systems: Specification, Springer-Verlag, 1992.

<sup>[</sup>MP95] Z. Manna, A. Pnueli, The Temporal Logic of Reactive and Concurrent Systems: Safety, Springer-Verlag, 1995.

Différents types d'objectifs de contrôle peuvent être considérés : assurer l'invariance, l'atteignabilité ou l'attractivité d'un ensemble d'états, etc. Les objectifs de contrôle peuvent également traduire un critère qualitatif et non plus logique. Ils s'expriment alors comme des relations d'ordre ou comme un critère de minimisation sur une trajectoire bornée du système.

Les différentes mises en œuvre réalisées sont surtout axées sur l'intégration des différents algorithmes induits par les objectifs de contrôle dans le système de calcul formel Sigali, mais sont également axés sur l'intégration de Sigali dans l'environnement Signal de manière à faciliter les preuves de programmes et la synthèse d'objectifs de commande.

## 4 Domaines d'applications

#### 4.1 Panorama

Mots clés : conception synchrone, télécommunication, traitement temps réel du signal, énergie, transport, avionique, automobile.

Résumé: Les recherches sur les méthodes de développement d'applications ne sauraient se concevoir sans une confrontation avec des applications, pour identifier en amont les problèmes rencontrés par les concepteurs (utilisateurs potentiels de nos techniques) et pour valider en aval les solutions proposées. C'est ainsi que le projet EP-ATR s'est impliqué très tôt dans des travaux liés aux télécommunications. En outre, il a été longtemps engagé dans une coopération avec EDF sur l'utilisation des techniques synchrones dans le domaine de l'énergie. D'autres domaines ont été abordés, en particulier une application en traitement radar infra-rouge a été traitée.

Dans le cadre du projet Sacres puis du projet SafeAir, les applications considérées relèvent du domaine de l'avionique. Le domaine des applications automobiles a également été abordé à travers le projet AEE.

#### 4.2 Télécommunications

Participants: Albert Benveniste, Paul Le Guernic, Jean-Pierre Talpin, Yunming Wang.

Mots clés: Signal, télécommunication, communication synchrone/asynchrone, conception objet.

**Résumé:** Nos activités dans le domaine des télécommunications sont issues d'une longue collaboration avec le Cnet, d'où provient le développement initial du langage Signal. Elles se sont poursuivies dans le cadre du projet Cairn autour des langages Signal et Alpha, ainsi que dans de nouvelles collaborations dans lesquelles l'utilisation mixte des modèles synchrone et asynchrone est étudiée.

L'industrie des télécommunications est, de plus en plus, soumise à de fortes contraintes qui demandent un effort important visant à maximiser la généricité des solutions proposées et à raccourcir les délais de mise sur le marché des produits. La diversité que l'on rencontre dans les applications développées nécessite la mise en œuvre de techniques variées pour répondre

aux problèmes rencontrés. Les techniques synchrones peuvent fournir des solutions partielles qu'il convient d'intégrer dans des méthodes de conception plus globales.

Issu d'une longue collaboration avec le Cnet, le langage Signal a d'abord été développé dans le cadre d'applications en traitement du signal. Le projet Cairn («Codesign d'Applications Irrégulières et Régulières par Niveaux») nous a permis, en collaboration avec le projet Api de l'Irisa, d'étendre les thèmes abordés à la conception de composants supportant des algorithmes qui comportent du calcul numérique intensif (image ou signal) et du contrôle complexe.

La taille et la complexité des applications mises en œuvre, la nécessité d'obtenir des spécifications et des programmes génériques, destinés à des configurations diverses fonctionnant dans des contextes hétérogènes, conduisent à mettre en œuvre des outils de conception fondés sur l'approche objet. Dans le cadre de cette approche, la complexité des interactions et les contraintes temps réel sont traitées à l'aide de descriptions de comportements faisant appel à des modèles d'automates. L'étude de l'utilisation de l'approche synchrone dans ce contexte a d'abord été entreprise en collaboration avec les Laboratoires de Marcoussis par la définition d'un modèle d'interaction entre des objets (décrits dans le langage Spoke) et des processus (décrits dans le langage Signal). Elle s'est poursuivie ensuite avec Alcatel, dans le cadre de l'action Reutel-2000 qui visait notamment à maîtriser la conception objet d'applications mises en œuvre selon des techniques mêlant les modèles synchrone et asynchrone.

## 4.3 Énergie

Participants: Fernando Jiménez Fraustro, Hervé Marchand, Sophie Pinchinat.

Mots clés : énergie, méthode formelle, programmation synchrone, automatismes industriels.

**Résumé :** Nos activités dans le domaine de l'énergie se sont situées depuis plusieurs années dans le cadre de coopérations avec EDF, prolongées à travers le projet européen Syrf. Elles concernent notamment la vérification et la synthèse de contrôleurs, mais aussi la simulation de systèmes hybrides.

Dans le domaine de la production et de la distribution d'énergie, en particulier électrique, on est en présence de systèmes dont :

- La sécurité est un caractère essentiel; elle concerne divers aspects des systèmes de contrôle :

- le service fourni peut avoir des aspects critiques dans la nature de ceux à qui il est destiné (par exemple les hôpitaux),

- le matériel lui-même est soumis à des conditions de fonctionnement dont le dérèglement peut entraîner des dommages fatals,

- enfin les techniques utilisées peuvent comporter un risque pour l'environnement dans lequel s'effectue l'activité.

Dans ces conditions, les systèmes qui contrôlent la production et la distribution d'énergie posent des problèmes qui sont du domaine d'application de nos techniques d'analyse et de vérification de comportement.

- La complexité est grande :

- que ce soit dans le cas de réseaux de distribution, constitués de contrôleurs de transformateurs interconnectés,

ou bien de contrôleurs de centrale électrique, où les capteurs à prendre en compte et les actionneurs auxquels fournir une commande se comptent par centaines, voire milliers, et où les architectures sur lesquelles le contrôle s'exécute comprennent des réseaux d'automates programmables en parallèle.

La conception et l'analyse de ces systèmes requièrent le support d'outils automatisés pour la construction de modèles et le calcul de mises en œuvre correctes vis-à-vis de la spécification. Elles doivent exploiter la particularité d'architectures à base d'automates programmables, comme il en est construit par Siemens, avec qui nous coopérons dans le projet européen SafeAir.

– L'héritage des spécifications de contrôleurs obéit à une culture particulière : les langages de spécification des contrôleurs ont été utilisés pour la conception de systèmes de taille importante, et récrire ces systèmes dans un langage nouveau n'est guère envisageable. Il s'agit de langages à base d'automates communicants, ou d'autres de type blocs-diagrammes et circuits d'opérateurs. Dans un but de meilleure acceptation des méthodes formelles par les utilisateurs, et de réutilisation du fonds des développements antérieurs, il est intéressant de travailler à l'intégration de ces langages aux techniques que nous proposons, sous la forme de leur encodage, et d'une traduction automatique dans un format synchrone.

## 4.4 Avionique

Participants : Albert Benveniste, Loïc Besnard, Abdoulaye Elhadji Gamatié, Thierry Gautier, Paul Le Guernic.

Mots clés: conception synchrone, Statecharts, Scade, Arinc.

**Résumé:** Nos activités dans le domaine de l'avionique se sont développées depuis plusieurs années dans le cadre de projets européens, notamment Sacres et SafeAir. Elles concernent tous les aspects du processus de développement, et en particulier la génération de code sur une architecture temps réel.

Le domaine de l'avionique est clairement un domaine critique pour les systèmes enfouis, où les industries de pointe sont confrontées à une exigence de sécurité maximale. L'industrie européenne est particulièrement bien placée dans ce secteur et doit conserver et améliorer ses atouts pour répondre à la forte augmentation actuelle en fonctionnalité et en complexité. L'avionique est donc un domaine d'application privilégié pour les méthodes formelles en général et spécialement la technologie synchrone.

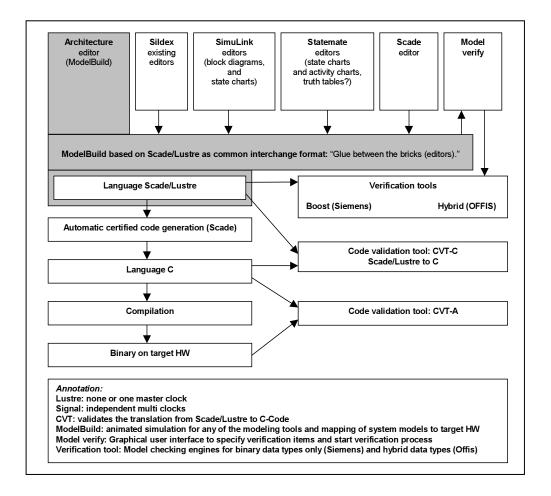

Dans le cadre de plusieurs projets européens successifs, nous avons été amenés à collaborer étroitement avec des industriels clés du domaine. Il s'agit des projets Synchron, Sacres (voir http://www.tni.fr/sacres), Syrf, et aujourd'hui SafeAir (voir section 7.3). La conception de systèmes avioniques s'appuie d'ores et déjà sur un processus de développement suivant le «cycle en V», sur l'emploi de technologies innovantes (utilisation des outils Statemate, Scade, Simulink, par exemple), sur l'utilisation de librairies temps réel standards (Arinc), sur le res-

pect de normes de certification (DO-178B). L'objectif d'un projet comme SafeAir, qui se base sur l'utilisation de ces technologies, est de permettre de réduire de 35 à 40% l'effort de développement des systèmes logiciels aéronautiques, tout en augmentant leur fiabilité : passage du «cycle en V» vers un «cycle en Y», en utilisant des méthodes de conception de haut niveau et des outils de génération automatique de code et de vérification formelle.

## 5 Logiciels

Polychrony pour Signal

## 5.1 Environnement de programmation Polychrony pour Signal

**Mots clés**: Signal, programmation synchrone, format commun, DC+, transformation de programme, Sildex.

Contact: L. Besnard.

**Résumé :** Le développement d'un environnement de programmation Signal, construit à l'Irisa selon des techniques de conception modulaires, répond à trois objectifs :

- a) il nous permet d'étudier des extensions sémantiques ou algorithmiques du modèle synchrone;

- b) il nous permet de mieux comprendre les applications et de dégager ainsi des problématiques nouvelles;

- c) il est diffusé à des fins d'expérimentation et d'enseignement dans des laboratoires pour lesquels la version commerciale Sildex ne convient pas.

L'environnement de programmation Signal, appelé Polychrony, se compose d'un ensemble de fonctionnalités de compilation et d'un éditeur graphique orienté blocs-diagrammes. Il doit être vu comme une «boîte à outils» synchrone. L'éditeur de Signal permet à l'utilisateur de construire ses programmes sous forme à la fois textuelle et graphique. L'existence de cet éditeur est un vecteur majeur pour la diffusion.

Les fonctionnalités de compilation sont écrites en C++ et C Ansi. L'éditeur graphique est écrit en Java (utilisation de la librairie Swing), C++ et Signal. Ceci permet d'avoir une version commune de l'environnement Signal dans les mondes Windows et Unix.

### Environnement de compilation

L'environnement de compilation Signal est un outil interactif de conception d'applications. L'architecture de l'environnement peut être vue comme un ensemble de services. Un service peut être ou non appliqué selon l'objectif : simulation, vérification formelle, compilation séparée, génération de code distribué, etc. Ces fonctionnalités sont accessibles au moyen d'options pour le compilateur «batch» et de manière interactive sous l'éditeur graphique. Le superviseur de l'environnement est lui-même un programme Signal.

Ces fonctionnalités s'appliquent également au format commun de la programmation synchrone (DC+). Ce format DC+, issu des travaux des projets européens Synchron et Sacres, permet de représenter, par delà un langage particulier, la paradigme «flots de données synchronisés». Il constitue aussi un format concret, servant de vecteur commun de représentation, pour des programmes ou des propriétés sur lesquels on souhaite appliquer des transformations définies dans le cadre du modèle synchrone.

Un programme Signal/DC+ est représenté de façon interne par un GHDC (graphe hiérarchisé aux dépendances conditionnées) qui constitue donc la structure principale de l'environnement.

On peut distinguer:

- un ensemble de traitements qui produisent un graphe hiérarchisé à partir d'un source Signal ou DC+;

- un ensemble de transformations du graphe hiérarchisé, transformations qui restituent un graphe hiérarchisé; ceci constitue le cœur du compilateur;

- un ensemble de traitements qui produisent les sources d'autres outils.

**Production du graphe.** L'ensemble des fonctionnalités pour la production du GHDC est constitué :

- de l'analyse syntaxique et contextuelle, qui fournit la représentation interne d'un programme source, Signal ou DC+, sous forme d'un arbre de syntaxe abstraite;

- de la production de graphe, qui associe à tout programme un graphe caractérisé par un système d'équations d'horloges. À ce stade, aucune vérification sur le système d'équations ni sur le graphe (cycles...) n'est effectuée.

**Transformations du graphe.** L'ensemble de traitements qui transforment le graphe hiérarchisé est constitué :

- de la compilation, dont le rôle principal est de triangulariser le système d'équations d'horloges et de détecter la présence de cycles de dépendance de données. Cette transformation permet la vérification partielle de la correction du programme vis-à-vis de ses synchronisations. La synthèse partielle d'expressions explicites du contrôle se traduit en une forêt d'arbres d'horloges, dont les racines sont éventuellement arguments de contraintes non résolues, et les nœuds internes des expressions explicites. Cette représentation sous forme de forêt d'arbres d'horloges (événements) correspond au format DC+. Pour ce calcul d'horloges, nous avons développé une structure hiérarchique de BDD qui s'avère très performante; nous utilisons actuellement le package BDD de Berkeley.

- des transformations inter-formats définies dans le cadre du projet Sacres. Ces transformations, décrites d'abord sur le format DC+, sur les différents niveaux de sous-formats ayant été identifiés, s'appliquent sur la forme interne d'un programme Signal (GHDC). Les différents sous-formats caractérisent une forme particulière du GHDC.

- Ainsi, le sous-format bDC+ (pour «boolean DC+»), dans lequel les horloges, représentées comme des flots booléens, sont organisées en une hiérarchie pour laquelle il existe une horloge maîtresse, est le point d'entrée adéquat pour des outils s'appuyant sur la hiérarchie des horloges, comme par exemple des générateurs de code.

- Le sous-format sbDC+ (pour «sequentialized boolean DC+») est le format d'entrée effectif des générateurs de code. Il est produit pour les programmes (bDC+) sans cycles et sans

contraintes. Un code sbDC+ est une liste de nœuds ordonnés selon les dépendances implicites et explicites du programme Signal-DC+. Ceci permet d'écrire de nouveaux générateurs de code sans avoir à parcourir le graphe du programme.

Le sous-format STS (pour «Symbolic Transition Systems») de bDC+, dans lequel la hiérarchie des horloges est plate (le statut présent/absent d'un signal est défini à tout instant par un booléen), est utilisé en entrée d'outils de vérification.

Le sous-format DC est un sous-format mono-horloge de STS.

Les transformations inter-formats,  $DC+ \rightarrow DDC+$ ,  $DC+ \rightarrow SBDC+$ ,  $DC+ \rightarrow STS$  et STS  $\rightarrow$  DC sont des fonctionnalités de l'environnement. Elles sont appliquées selon l'objectif de la compilation.

#### - de l'application du principe de substitution du langage. On peut ${ m citer}$ :

- la transformation des booléens (opérateur logiques et relationnels) en événements;

cette opération peut être utile au calcul d'horloges afin de prouver des équivalences;

- la suppression des renommages (équations de définition triviales);

- l'unification des signaux définis par la même expression;

- la substitution des signaux référencés au plus N fois dans le programme (N étant un paramètre de compilation), par leur expression de définition.

- des opérations de partitionnement de graphe, qui produisent un graphe constitué de nœuds représentant eux-mêmes des graphes. On peut citer :

- la séparation contrôle/calculs, qui consiste à séparer la partie contrôle de l'application de la partie calcul.

- la séparation état/reste, qui consiste à séparer la partie état du programme du reste de l'application.

- le calcul de lignées sur entrées, qui consiste à partitionner un graphe selon le critère qualitatif suivant : deux nœuds sont éléments de la même lignée sur entrée si et seulement s'ils sont précédés du même sous-ensemble d'entrées. Ce partitionnement est à la base d'un nouveau schéma de génération de code séquentiel : une lignée peut être exécutée de manière atomique dès que ses entrées sont disponibles.

- la répartition de programmes, qui se base sur l'utilisation de pragmas pour l'affectation des nœuds à des unités de calcul.

#### - des calculs systèmes suivants :

- la synthèse d'interface, dont le but est l'extraction d'éléments de la représentation interne en vue de la compilation séparée de programmes Signal. Cette opération consiste en le calcul de la fermeture transitive du graphe réduite aux entrées/sorties du processus compilé.

- le retiming, qui consiste en la réécriture de toute fonction synchrone construite sur les expressions de retard afin d'une part, de faire apparaître des variables d'état booléennes et d'autre part, de réduire le nombre des variables d'état.

#### Production de code Cet ensemble est constitué :

- de la génération de code séquentiel, qui passe par un tri topologique du graphe et qui produit du code C ou c++;

- de la restitution de source Signal, qui fournit à l'utilisateur le GHDC sous la forme d'un nouveau programme Signal faisant apparaître la hiérarchie obtenue et les synchronisa-

tions calculées. La restitution du source peut également être effectuée en partant d'une représentation sous forme d'arbre de syntaxe abstraite.

- de la restitution de source DC+, ceci afin de pouvoir se connecter aux outils disponibles autour du format.

- de l'interfaçage avec des systèmes de preuves; actuellement la connexion avec l'outil Sigali est réalisée dans le but d'étudier les propriétés dynamiques des programmes (décompilateur Z/3Z).

- les calculs d'architectures; actuellement la connexion avec l'outil Syndex est réalisée. L'outil Syndex (Y. Sorel, projet Sosso à Rocquencourt) permet d'effectuer une implantation optimisée sous contraintes temps réel sur une architecture multi-processeur.

#### Diffusion du logiciel

La version commerciale de Signal est vendue par TNI sous la forme de l'environnement Sildex. La version Inria de Signal, qui jusqu'à cette année pouvait être obtenue dans le cadre d'une convention de mise à disposition gratuite signée pour un an renouvelable sera bientôt accessible, en accès libre, sur le site Web du projet Espresso, successeur du projet EP-ATR, dans le cadre du nouvel environnement Polychrony.

Signal est actuellement mis à disposition dans des écoles ou universités (Ubo, IUP de Lorient, université de Nantes Irin, Supelec, Oil & Gas University of Ploiesti — Pologne, University of Victoria — Canada, University of Michigan — USA, Mecaprom — Mexique), et chez certains industriels pour des études ou évaluations particulières (EDF). Notre objectif est de fournir à court terme une distribution sous une licence de type logiciel libre (voir section 6.1).

#### 5.2 Sigali

**Mots clés** : Signal, DC+, Sigali, système dynamique polynomial, vérification, synthèse de contrôleur.

Contacts: L. Besnard, H. Marchand.

**Résumé :** Sigali est un système de calcul formel permettant la vérification de propriétés de programmes Signal ou DC+.

Sigali est un système de calcul formel interactif spécialisé dans les calculs algébriques sur l'anneau  $\mathbb{Z}/3\mathbb{Z}[X]$ . Il est destiné à la vérification des propriétés statiques et dynamiques de programmes Signal ou  $\mathrm{DC}+[1,2]$  et plus généralement de tout système dynamique polynomial dans  $\mathbb{Z}/3\mathbb{Z}[X]$ . Il permet également la synthèse de contrôleurs de systèmes à événements discrets. L'adjonction de primitives de création et de manipulation de fonctions à valeurs entières autorise les calculs de commande optimale.

Sigali est un logiciel déposé à l'APP sous le numéro IDDN.FR.001.370006.S.P.1999.000.10600. Comme pour l'environnement Polychrony, Sigali peut être obtenu actuellement après signature d'une convention de mise à disposition.

#### 6 Résultats nouveaux

Nos thèmes de recherche introduits en 2.4 ont donné lieu aux résultats décrits dans les sections suivantes :

- les sections 6.1 à 6.4 relèvent de la «Description d'applications» (2.4.1);

- les sections 6.5 et 6.6 concernent l'«Étude des propriétés des processus synchrones» (2.4.2);

- les sections 6.7 à 6.9 portent sur des «Méthodes et outils pour la conception d'architectures de mise en œuvre» (2.4.3).

## 6.1 Évolutions de Signal et de son environnement

Mots clés : programmation synchrone, Signal, transformation de programme, compilation séparée, évaluation de performance.

**Participants** : Loïc Besnard, Patricia Bournai, Thierry Gautier, Paul Le Guernic, Laurent Vibert.

**Résumé :** La version actuellement diffusée de Signal, Signal V4, a été définie en coopération avec la société TNI (François Dupont), qui développe et commercialise l'environnement Sildex issu des travaux sur Signal. Elle est progressivement enrichie dans le sens d'une meilleure expressivité, et son environnement est amélioré de manière à en assurer une diffusion plus large.

## Évolutions du langage

Nous avons précisé la notion d'«affectation multiple» (syntaxique) de signaux qui avait été introduite l'an passé dans le langage Signal. Une équation de définition partielle  $X:=E_i$  se récrit en l'équation flot de données  $X:=E_i$  default X. Différentes expressions  $E_i$  définissant X dans des équations de définition partielle doivent avoir la même valeur à leurs instants communs lorsqu'elles ont des instants communs. L'horloge de X est plus grande que la borne supérieure des horloges des expressions  $E_i$  définissant X. Il est possible de compléter la définition de X par une valeur par défaut (qui peut être une constante) lorque les  $E_i$  sont absents.

Nous avons également introduit une notion de variables d'état (statevar), représentées par des signaux dont l'horloge est plus grande que la borne supérieure des horloges de tous les signaux de l'unité de compilation dans laquelle la variable d'état est déclarée. Les variables d'état sont définies exclusivement par des équations de définition partielle, qui définissent, à une horloge donnée, les valeurs suivantes de la variable d'état. L'occurrence d'une variable d'état dans une expression permet d'accéder à sa valeur au début du step courant.

Combinées avec l'extension de la visibilité des signaux et avec l'intégration de la structure case, ces extensions permettent notamment une spécification plus souple des automates en Signal. L'introduction de ces notions nous a permis par exemple de simplifier l'écriture du programme Signal qui supervise l'environnement Signal.

Le symbole de définition flot de données, :=, induit une relation de dépendance entre l'expression de partie droite et le signal défini. Nous avons introduit un nouveau symbole, noté := :, qui permet de spécifier des définitions non orientées. Une équation X := E se traduit

alors par la composition  $X := E \mid E --> X$ . La sémantique de traces de Signal s'exprime sur des équations non orientées (en cours d'écriture dans la nouvelle version du manuel de référence du langage).

De manière proche de ce que permet le langage Esterel, nous considérons qu'il existe un tick pour tout processus Signal, qui est un signal dont l'horloge est plus grande que la borne supérieure des horloges de tous les signaux du processus. Ce tick peut être désigné en Signal à travers l'étiquette pouvant être associée à un processus.

Nous distinguons alors différentes classes syntaxiques de processus :

- la fonction : sans état, synchrone sur ses entrées-sorties, toute entrée précède toute sortie ;

- le  $n \alpha u d$  (à la Lustre) : endochrone, le tick appartient aux entrées-sorties, toute entrée précède toute sortie;

- l'action : le tick est externe, toute entrée précède toute sortie ;

- le *processus* : le plus général, exochrone.

#### Compilation séparée

La compilation séparée de différents modules agissant entre eux est un besoin de plus en plus important pour une utilisation dans de larges applications. À la différence de [NTGL97], les modules que nous lions dynamiquement ne dépendent pas l'un de l'autre via une interface de foncteur, mais partagent juste un ensemble de signaux. Pour que ce partage puisse avoir lieu sans gêner la compilation séparée, il faut trouver des contraintes pertinentes sur les horloges de ces signaux.

Partant d'une algèbre de processus minimale, on élabore un ensemble de contraintes d'horloges pour chacun des modules. Pour que deux processus P et Q partageant un signal  $^x$  puissent être liés, il faut que l'horloge de ce signal x ne soit pas gardée par des contraintes contradictoires, c'est-à-dire que l'on puisse prouver que x ne peut pas être à la fois présent dans P et absent dans Q.

À plus long terme, on essaiera d'étendre les techniques de compilation séparée à la génération dynamique de processus synchrone, et de l'appliquer à un calcul objet tel que celui développé par M. Kerbœuf et J.-P. Talpin (voir section 6.3).

#### **Environnement Signal**

Outre l'introduction des notions nouvelles décrites ci-dessus, nous avons également défini et mis en œuvre cette année des algorithmes de morphismes de programmes Signal : pour un programme P et une description de la transformation (module Signal qui décrit pour tout opérateur la transformation qui lui est associée), un nouveau programme (image de P) est automatiquement engendré. Ce principe a été appliqué pour l'extraction de propriétés temporelles [6, 27] dans le cadre du projet SafeAir. Pour cela, à partir du programme source, correspondant à la spécification fonctionnelle d'un système, on engendre automatiquement son image «temporelle» par une interprétation; cette image est un processus Signal qui consiste à

<sup>[</sup>NTGL97] D. NOWAK, J. TALPIN, T. GAUTIER, P. LE GUERNIC, « An ML-like module system for the synchronous language Signal », in: European Conference on Parallel Processing (Euro-Par'97), Springer-Verlag, LNCS 1300, p. 1244-1253, 1997, ftp://ftp.irisa.fr/local/signal/publis/ articles/EuroPar-97:modul.ps.gz.

mettre à jour les dates de disponibilité des entrées afin de produire les dates de disponibilité des sorties. La mise à jour des dates est faite de manière à prendre en compte les facteurs tels que les délais des opérations individuelles (dépendants de l'architecture cible) et le flot d'exécution (dépendant du contrôle de l'application).