# **Activity Report 2011**

# **Project-Team CAIRN**

# Energy Efficient Computing ArchItectures with Embedded Reconfigurable Resources

IN COLLABORATION WITH: Institut de recherche en informatique et systèmes aléatoires (IRISA)

RESEARCH CENTER

Rennes - Bretagne-Atlantique

THEME **Architecture and Compiling**

# **Table of contents**

| 1. | Members                                                                                     | 1  |  |  |  |  |

|----|---------------------------------------------------------------------------------------------|----|--|--|--|--|

| 2. |                                                                                             |    |  |  |  |  |

|    | 2.1. Overall Objectives                                                                     |    |  |  |  |  |

|    | 2.2. Highlights                                                                             | 4  |  |  |  |  |

| 3. | Scientific Foundations                                                                      | 4  |  |  |  |  |

| ٥. | 3.1. Panorama                                                                               |    |  |  |  |  |

|    | 3.2. Dynamically and Heterogeneous Reconfigurable Platforms                                 | -  |  |  |  |  |

|    | 3.3. Compilation and Synthesis for Reconfigurable Platform                                  | 6  |  |  |  |  |

|    | 3.4. Algorithm Architecture Interaction                                                     | 7  |  |  |  |  |

| 4. | Application Domains                                                                         | 7  |  |  |  |  |

| •• | 4.1. Panorama                                                                               | 7  |  |  |  |  |

|    | 4.2. 4G Wireless Communication Systems                                                      | 8  |  |  |  |  |

|    | 4.3. Wireless Sensor Networks                                                               | 8  |  |  |  |  |

|    | 4.4. Multimedia processing                                                                  | 8  |  |  |  |  |

| 5. | Software                                                                                    | 8  |  |  |  |  |

| ٠. | 5.1. Panorama                                                                               | ۶۶ |  |  |  |  |

|    | 5.2. Gecos                                                                                  | C  |  |  |  |  |

|    | 5.3. ID.Fix: Infrastructure for the Design of Fixed-point Systems                           | 10 |  |  |  |  |

|    | 5.4. UPaK: Abstract Unified Pattern-Based Synthesis Kernel for Hardware and Software System |    |  |  |  |  |

|    | 5.5. DURASE: Automatic Synthesis of Application-Specific Processor Extensions               | 11 |  |  |  |  |

|    | 5.6. PowWow: Power Optimized Hardware and Software FrameWork for Wireless Motes (AP         |    |  |  |  |  |

|    | 10-01)                                                                                      | 11 |  |  |  |  |

|    | 5.7. SoCLib: Open Platform for Virtual Prototyping of Multi-Processors System on Chip       | 12 |  |  |  |  |

|    | 5.8. OCHRE: On-Chip Randomness Extraction                                                   | 12 |  |  |  |  |

| 6. | New Results                                                                                 | 13 |  |  |  |  |

| •  | 6.1. Dynamically and Heterogeneous Reconfigurable Platforms                                 | 13 |  |  |  |  |

|    | 6.1.1. New Reconfigurable Architectures                                                     | 13 |  |  |  |  |

|    | 6.1.1.1. Power models of reconfigurable architectures                                       | 13 |  |  |  |  |

|    | 6.1.1.2. High-level modeling of reconfigurable architectures                                | 13 |  |  |  |  |

|    | 6.1.1.3. Reconfiguration controller                                                         | 14 |  |  |  |  |

|    | 6.1.2. Management of Dynamically Reconfigurable Systems                                     | 14 |  |  |  |  |

|    | 6.1.2.1. Spatio-Temporal Scheduling based on Artificial Neural Networks                     | 14 |  |  |  |  |

|    | 6.1.2.2. Flexible Communication OS Service                                                  | 14 |  |  |  |  |

|    | 6.1.3. Fault-Tolerant Reconfigurable Architectures                                          | 15 |  |  |  |  |

|    | 6.1.4. Low-Power Architectures                                                              | 15 |  |  |  |  |

|    | 6.1.4.1. Ultra Low-Power Architecture for Control-Oriented Applications in Wireless Sen     |    |  |  |  |  |

|    | Nodes                                                                                       | 15 |  |  |  |  |

|    | 6.1.4.2. Wakeup Time and Wakeup Energy Estimation in Power-Gated Logic Clusters             | 15 |  |  |  |  |

|    | 6.1.5. Arithmetic Operators for Cryptography                                                | 16 |  |  |  |  |

|    | 6.1.5.1. ECC Processor with Protections Against SCA                                         | 16 |  |  |  |  |

|    | 6.1.5.2. Arithmetic Operators for High-Performance Cryptography                             | 16 |  |  |  |  |

|    | 6.1.6. SoC Modeling and Prototyping on FPGA-based Systems                                   | 16 |  |  |  |  |

|    | 6.2. Compilation and Synthesis for Reconfigurable Platform                                  | 17 |  |  |  |  |

|    | 6.2.1. Polyhedral based loop transformations for High-Level synthesis                       | 17 |  |  |  |  |

|    | 6.2.2. Reconfigurable Processor Extensions Generation                                       | 17 |  |  |  |  |

|    | 6.2.3. Run-time Reconfigurable Architecture Modeling                                        | 18 |  |  |  |  |

|    | 6.2.4. Floating-Point to Fixed-Point Conversion                                             | 18 |  |  |  |  |

|    | 6.3. Algorithm Architecture Interaction                                                     | 18 |  |  |  |  |

|    | 6.3.1. Flexible hardware accelerators for biocomputing applications                         | 18 |  |  |  |  |

|     | 6.3.2. Range Estimation and Computation Accuracy Optimization                    | 19 |

|-----|----------------------------------------------------------------------------------|----|

|     | 6.3.2.1. Range Estimation                                                        | 19 |

|     | 6.3.2.2. Accuracy and performance evaluation                                     | 19 |

|     | 6.3.3. Reconfigurable Video Coding                                               | 19 |

|     | 6.3.4. Multi-Antenna Systems                                                     | 20 |

|     | 6.3.5. Cooperative Strategies for Low-Energy Wireless Networks                   | 20 |

|     | 6.3.6. Opportunistic Routing                                                     | 21 |

|     | 6.3.7. Adaptive techniques for WSN power optimization                            | 21 |

| 7.  | Contracts and Grants with Industry                                               | 22 |

|     | 7.1. ANR Ingénérie Numérique et Sécurité - ARDyT (2011-2015)                     | 22 |

|     | 7.2. ANR Ingénérie Numérique et Sécurité - COMPA (2011-2015)                     | 22 |

|     | 7.3. ANR Ingénérie Numérique et Sécurité - DEFIS (2011-2015)                     | 23 |

|     | 7.4. ANR ARPEGE - GRECO (2010-2013)                                              | 23 |

|     | 7.5. Images and Networks competitiveness cluster - 100GFlex project (2010-2013)  | 23 |

|     | 7.6. NANO2012 Program - S2S4HLS (2008-2012)                                      | 23 |

|     | 7.7. NANO2012 Program - RecMotifs (2008-2012)                                    | 24 |

|     | 7.8. ANR Architectures du Futur Open-People (2009-2012)                          | 24 |

|     | 7.9. ANR BioWiC (2009-2011)                                                      | 24 |

|     | 7.10. ANR Architectures du Futur - CIFAER (2008-2011)                            | 25 |

|     | 7.11. ANR Architectures du Futur - FOSFOR (2008-2011)                            | 25 |

| 8.  | Partnerships and Cooperations                                                    | 25 |

|     | 8.1. Regional Initiatives                                                        | 25 |

|     | 8.2. National Initiatives                                                        | 25 |

|     | 8.3. European Initiatives                                                        | 26 |

|     | 8.3.1. FP7 Projects                                                              | 26 |

|     | 8.3.2. Collaborations in European Programs, except FP7                           | 27 |

|     | 8.3.3. Major European Organizations with which Cairn has followed Collaborations | 27 |

|     | 8.4. International Initiatives                                                   | 28 |

|     | 8.4.1. INRIA Associate Teams                                                     | 28 |

|     | 8.4.2. INRIA International Partners                                              | 28 |

|     | 8.5. Exterior research visitors                                                  | 29 |

| 9.  | Dissemination                                                                    |    |

|     | 9.1. Animation of the Scientific Community                                       | 29 |

|     | 9.2. Seminars and Invitations                                                    | 30 |

|     | 9.3. Teaching and Responsibilities                                               | 31 |

|     | 9.3.1. Teaching Responsibilities                                                 | 31 |

|     | 9.3.2. Teaching                                                                  | 31 |

|     | 9.3.3. HDR and PhD                                                               | 32 |

| 10. | Bibliography                                                                     | 34 |

**Keywords:** Hardware Accelerators, Compiling, Embedded Systems, Energy Consumption, Parallelism, Sensor Networks, Security, Signal Processing, Reconfigurable Architectures, Systemon-Chip, High-Level Synthesis, Arithmetic Operators, Wireless Communications, Cooperative Communications

CAIRN is a common project with CNRS, University of Rennes 1 (ENSSAT Lannion and ISTIC/ESIR Rennes) and ENS Cachan-Antenne de Bretagne, and is located on two sites: Rennes and Lannion. The team has been created on January the 1<sup>st</sup>, 2008 and is a "reconfiguration" of the former R2D2 research team from Irisa.

## 1. Members

#### **Research Scientists**

François Charot [Research Associate (CR) Inria, Rennes]

Steven Derrien [Associate professor, University of Rennes 1, ISTIC, on leave at Inria since Sept. 2009, Rennes, HdR]

Daniel Menard [Associate professor, University of Rennes 1, ENSSAT, on leave at Inria since Sept. 2011, Lannion, HdR]

Olivier Sentieys [Team Leader, Professor, University of Rennes 1, ENSSAT, on leave (half time) at Inria, Lannion, HdR]

Arnaud Tisserand [Research Associate (CR) CNRS, Lannion, HdR]

#### **Faculty Members**

Olivier Berder [Associate professor, University of Rennes 1, ENSSAT, Lannion]

Emmanuel Casseau [Professor, University of Rennes 1, ENSSAT, Lannion, HdR]

Daniel Chillet [Associate professor, University of Rennes 1, ENSSAT, Lannion, HdR]

Sébastien Pillement [Associate professor, University of Rennes 1, IUT, Lannion, HdR]

Matthieu Gautier [Associate professor, University of Rennes 1, IUT, Lannion, since Nov. 2011]

Patrice Quinton [Professor, Director of the Brittany branch of the ENS de Cachan, Rennes, HdR]

Romuald Rocher [Associate Professor, University of Rennes 1, IUT, Lannion]

Pascal Scalart [Professor, University of Rennes 1, ENSSAT, Lannion, HdR]

Christophe Wolinski [Professor, University of Rennes 1, Director of ESIR, Rennes, HdR]

Stanislaw Piestrak [Professor, on leave from University of Metz at Inria since Sept. 2008 until Aug. 2011, Lannion, HdR]

### **Technical Staff**

Charles Wagner [IR CNRS SED, until Aug. 2011, Rennes]

Philippe Quémerais [Research Engineer (half time), University of Rennes 1, ENSSAT, Lannion]

Arnaud Carer [100Gflex Project, Lannion]

Romain Fontaine [Perecap Project, Lannion]

Remi Pallas [POF Project, Lannion]

Nicolas Simon [DEFIS Project since Nov. 2011, Lannion]

Amit Kumar [Nano 2012 Project until Sept. 2011, Rennes]

Maxime Naullet [IJD INRIA KerGekoz Project, Rennes]

Manh Pham [Cifaer ANR Project until Dec. 2011, Lannion]

Vaibhav Bhatnagar [IC INRIA SNOW Project, Lannion]

#### PhD Students

Michel Thériault [CSRNG Canada grant (co-supervision with Laval University, Québec), Lannion]

Antoine Eiche [University grant, Lannion]

Quoc-Tuong Ngo [Region/CG22 University grant, Lannion]

Andrei Banciu [CIFRE grant, STMicroelectronics, Grenoble]

Karthick Parashar [Inria Cordi grant, Lannion]

Antoine Floch [Inria grant, Rennes]

Antoine Morvan [Inria grant, Rennes]

Naeem Abbas [Inria grant, Rennes]

Le Quang Vinh Tran [MENRT grant, Lannion]

Chenglong Xiao [Inria grant, Lannion]

Jean-Charles Naud [Inria grant, Lannion]

Matthieu Texier [CEA grant, Saclay]

Thomas Chabrier [Brittany Region/CG22 University grant, Lannion]

Danuta Pamula [Co-tutelle France-Poland, Lannion]

Robin Bonamy [University grant, Lannion]

Vivek D. Tovinakere [University grant, Lannion]

Mahtab Alam [University grant, Lannion]

Amine Didioui [CEA grant, Grenoble]

Hervé Yviquel [MENRT grant, Lannion]

Istas Pratomo [Indonesian Gov. grant, Lannion]

Aymen Chakhari [Brittany Region INRIA grant, Lannion]

Trong-Nhan Le [University grant, Lannion]

Pramod P. Udupa [University grant, Lannion]

Ganda-Stéphane Ouedraogo [MENRT grant, Lannion]

Karim Bigou [INRIA/DGA grant, Lannion]

Franck Bucheron [DGA grant, Rennes]

Romain Brillu [CIFRE grant, Thales, Palaiseau]

Riham Nehmeh [CIFRE grant, STMicroelectronics, Grenoble]

Quang-Hai Khuat [Brittany Region/CG22 University grant, Lannion]

#### **Post-Doctoral Fellows**

Ruifeng Zhang [Since Apr. 2010, Lannion]

Cécile Beaumin [ATER Univ. Rennes 1 since Oct. 2011, Lannion]

Ludovic Devaux [ATER Univ. Rennes 1 since Oct. 2011, Lannion]

Kevin Martin [ATER Univ. Rennes 1 until Aug. 2011, Rennes]

Quentin Meunier [NANO2012 Project until Aug. 2011, Lannion]

#### **Administrative Assistant**

Nadia Saintpierre [Assistant, INRIA, Rennes]

# 2. Overall Objectives

## 2.1. Overall Objectives

The scientific aim of CAIRN is to study hardware and software architectures of *Reconfigurable System-on-Chip* (RSoC), i.e. integrated chips which include reconfigurable blocks whose hardware configuration may be changed before or even during execution.

Reconfigurable systems have been considered by research in computer science and electrical engineering for about twenty years [95], [102] thanks to the possibilities opened up initially by Field Programmable Gate Arrays (FPGA) technology and more recently by reconfigurable processors [92], [3], [9]. In FPGA, a particular hardware configuration is obtained by loading a bit-stream that is used to shape parameterizable blocks into specific hardware functions. In a reconfigurable processor, coarse-grained logic elements operate on word-size operands and employ reconfigurable operators as computing elements. They are generally tightly coupled with one or more processor cores and act as reconfigurable computing accelerators. Usually, the configuration streams are small enough to ensure run-time – or dynamic – reconfiguration. In a broader sense, hardware reconfiguration may happen not only in a single chip, but also in a distributed hardware system, in order to adapt this system to changing conditions. This happens, for example, on a mobile system.

Recent evolutions in technology and modern hardware systems confirm that reconfigurable chips are increasingly used in modern applications or embedded into more general System-on-Chip (SoC) [116]. Rapidly changing application standards in fields such as communications and information security ask for frequent modifications of the devices. Software updates may often not be sufficient to keep devices in the market, but hardware redesigns are quite expensive. The need to continuously adapt to changing environments (e.g. cognitive radio) is another incentive to use dynamic reconfiguration at runtime. Finally, with technologies at 65 nm and below, manufacturing problems strongly influence electrical parameters of transistors, and transient errors caused by particles or radiations will also more and more often appear during execution: error detection and correction mechanisms or autonomic self-control can benefit from reconfiguration capabilities.

Standard processors or system-on-chip enable to develop flexible software on fixed hardware. Reconfigurable platforms enable to develop *flexible software on flexible hardware*.

As the density of chips increases [115], power efficiency has become "the Grail" of chip architects: not only for portable devices but also for high-performance general-purpose processors, power (or energy) considerations are as important as the overall performance of the products. This power challenge can only be tackled by using application-specific architectures, or at least by incorporating some application-specific elements into SoCs, as ASICs (Application Specific Integrated Circuit) are much more power-efficient than GPPs (General-Purpose Processor). The designers of SoCs thus face a very difficult challenge: trading between the flexibility of GPP which leads to high-volume and short design time, and the efficiency of ASICs which helps solving the power efficiency problem. Therefore, reconfigurable architectures are often recognized to exhibit the best trade-off potential between power, performance, cost and flexibility [114], [98] because their hardware structure can be adapted to the application needs.

However, reconfigurable systems raise several questions:

- What are the basic elements of a good reconfigurable system? In the early days, they were bit-level

operators, and they tend to become word-level operators. There is however no agreement on the

model that should be used.

- How can we reconfigure such a system quickly? When to reconfigure? What is the information needed to reconfigure?

- How can we program efficiently reconfigurable systems? We would like to have compilers, not hardware synthesizers and place-and-routers.

- In an application, what must be targeted to reconfigurable chips and what to conventional processors?

More generally, how can we transform and optimize an algorithm to take advantage of the potential of reconfigurable chips?

- How reconfigurable architectures can impact security of a complete SoC?

The scientific goal of CAIRN is to contribute to answer these questions, based on our background and past experience. To this end, CAIRN intends to approach energy efficient reconfigurable architectures from three angles: the invention of **new reconfigurable platforms**, associated **design and compilation tools**, and the exploration of the **interaction between algorithms and architectures**. Power consumption and processing power are considered as the main constraints in our proposed architecture, design flow and algorithm optimizations, in order to maximize the global energy efficiency of the system.

**Wireless Communication** is our privileged field of applications. Our research includes the prototyping of parts of these applications on reconfigurable and programmable platforms. Moreover in the framework of research and/or contractual cooperations other **application domains** are considered: bioinformatics, image indexing, video processing, operators for cryptography and traffic filtering in high-speed networks.

Members of the CAIRN team have collaborations with large companies like STmicroelectronics (Grenoble), Technicolor (Rennes), Thales (Paris), Alcatel (Lannion), France-Telecom Orange Labs (Lannion), Atmel (Nantes), Xilinx (USA), SME like Geensys (Nantes), R-interface (Marseille), TeamCast/Ditocom (Rennes), Sensaris (Grenoble), Envivio (Rennes), InPixal (Rennes), Sestream (Paris), Ekinops (Lannion) and Institute like DGA (Rennes), CEA (Saclay, Grenoble). They are involved in several national or international funded projects (FP7 Alma, FP7 Flextiles, ITEA2 Geodes, Nano2012 S2S4HLS and RECMOTIF projects, ANR funded Ardyt, Defis, Faon, Compa, BioWic, Open-People, Greco, Ocelot and "Images&Networks Competitiveness Cluster" funded 100Gflex).

## 2.2. Highlights

Daniel Menard and Steven Derrien defended their "Habilitation à Diriger des Recherches (HDR)" thesis in 2011.

## 3. Scientific Foundations

#### 3.1. Panorama

The development of complex applications is traditionally divided into three steps: theoretical study of the algorithms, study of the target architecture and implementation. When facing new emerging applications such as high-performance, low-power, low-cost mobile communication systems or smart sensor-based systems, it is mandatory to strengthen the design flow by a simultaneous study of both algorithmic and architectural issues<sup>1</sup>.

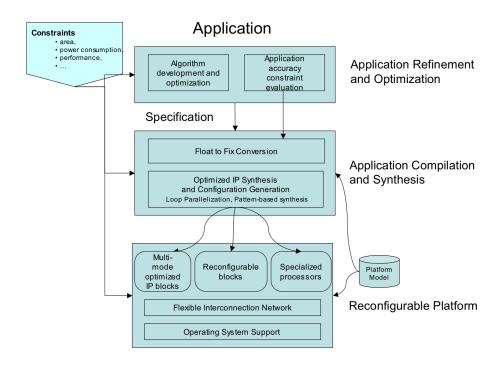

Figure 1. CAIRN's general design flow and related research themes

<sup>&</sup>lt;sup>1</sup>Often referenced as algorithm-architecture mapping or interaction.

Figure 1 shows the global design flow that we propose to develop. It is organized in levels which refer to our three research themes: application optimization (algorithmic, fixed-point and advanced representations of numbers), platform instance optimization (hardware and middleware), and stepwise refinement and compilation of software tasks (transformations, configuration generation).

In the rest of this part, we briefly describe the challenges concerning **new reconfigurable platforms** in Section 3.2, the issues on **compiler and synthesis tools** related to these platforms in Section 3.3, and the remaining challenges in **algorithm architecture interaction** in Section 3.4.

## 3.2. Dynamically and Heterogeneous Reconfigurable Platforms

One available technology for building reconfigurable systems is the field-programmable gate arrays (FPGA) introduced to the market in the mid 1980s. Today's components feature millions of gates of programmable logic, and they are dense enough to host complete computing systems on a programmable chip. These FPGAs have been the reconfigurable computing mainstream for a couple of years and achieve flexibility by supporting gate-level reconfigurability, e.g. they can be fully optimized for any application at the bit level. However, their flexibility is achieved at a very important interconnection cost. To be configured, a large amount of data must be distributed via a slow serial programming process to all the processing and interconnection resources. Configurations must be stored in an external memory. These interconnection and configuration overheads lead to energy inefficient architectures.

To increase optimization potential of programmable processors without the FPGAs penalties, the functional-level reconfiguration was introduced. *Reconfigurable Processors* are the most advanced class of reconfigurable architectures. The main concern of this class of architectures is to support flexibility while reducing reconfiguration overhead. Precursors of this class were the KressArray [103], RaPid [101], and RaW machines [118] which were specifically designed for streaming algorithms. Morphosys [106], Remarc [110] or Adres [99] contain programmable ALUs with a reconfigurable interconnect. These works have led to commercial products such as the Extreme Processor Platform (XPP) [91] from PACT, Bresca [113] from Silicon Hive, designed mainly for telecommunication applications.

Another strong trend towards heterogeneous reconfigurable processors can be observed. Hybrid architectures combine standard GPP or DSP cores with arrays of *field-configurable elements*. These new reconfigurable architectures are entering the commercial market. Some of their benefits are the following: functionality on demands (set-top boxes for digital TV equipped with decoding hardware on demand), acceleration on demand (coprocessors that accelerate computationally demanding applications in multimedia, communications applications), and shorter time to market (products that target ASIC platforms can be released earlier using reconfigurable hardware).

Dynamic reconfiguration allows an architecture to adapt itself to various incoming tasks. This requires complex management and control which can be provided as services of a real-time operating system (RTOS) [107]: communication, memory management, task scheduling [97] [94] and task placement [89]. Such an Operating System (OS) approach has many advantages: it is a complete design framework, independent of the technology and of the hardware architecture, thus helping to drastically reduce the design time of the complete platform.

Communications in a reconfigurable platform is also a very important research subject. The role of communication resources is to support transactions between the different components of the platform, either between macro-components of the platform – main processor, dedicated modules, dynamically reconfigurable parts of the platform – or inside the elements of the reconfigurable parts themselves. This has motivated studies on Networks on Chip for Reconfigurable SoCs [93] [112] that trade flexibility and quality of service.

In CAIRN we mainly target reconfigurable system-on-chip (RSoC) defined as a set of computing and storing resources organized around a flexible interconnection network and integrated onto a single silicon chip (or programmable chip such as FPGAs). The architecture is specialized for an application domain, and the flexibility is featured by hardware reconfiguration and software programmability. Therefore, computing resources are heterogeneous and we focus on the following:

- Reconfigurable hardware blocks with a dynamic behavior where reconfigurability can be

achieved at the bit or at the operator level. Our research aims at defining new reconfigurable computing and storing resources. Since reconfiguration must occur as fast as possible (typically a few

cycles), the reduction of the configuration bit-stream length is also a key issue.

- When performance and power consumption are major constraints, it is well known that optimized

specialized hardware blocks (often called IPs for Intellectual Properties) are the best (and often the

only) solution. As a flexible extension of specialized IPs, we study multi-mode components for

very specific set of high-complexity algorithms, without loss of performance.

- Specialized **processors with tailored instruction-set** still offer a viable solution to trade between energy efficiency and flexibility. They are especially interesting in the context of recent FPGA platforms where multiple processors can be easily embedded. We also focus on the automatic generation of an optimized customized instruction-set and of the associated data-path and interface with an embedded processor core.

## 3.3. Compilation and Synthesis for Reconfigurable Platform

The absence of compilers is one of the major limitations for the use of reconfigurable architectures in real-life applications. Therefore, the ability to compile and optimize code on reconfigurable hardware platforms from high-level specifications is the key for a real success story and is a hot topic in the research community. We continue our research efforts to offer **efficient tools with close links to architectures**.

Most current programming environments for reconfigurable systems consist of separate tool flows for the software and the hardware. Processor code and configuration data for the reconfigurable processing units are handcrafted and wrapped into libraries of functions. Progress beyond current practices calls for compilers capable of generating code and configurations from a high-level general-purpose programming language. Such a compiler decides which operations go into the reconfigurable processors. Loops or frequently executed code fragments are good candidates for reconfigurable platforms. For general-purpose code, this leads to several problems: it is difficult to extract sets of operations with matching granularity at a sufficient level of parallelism; inner loops of general-purpose programs often contain excess code; i.e. code that must be run on a CPU such as exceptions, function or system calls. Efforts aimed at automatic code generation for reconfigurable architectures include works of [111], [117] and [120].

Another approach to programming and design of reconfigurable platform, especially for special-purpose elements, is to use techniques inspired from high-level synthesis. Here also, loops are the target of the methods: the goal is to either generate special-purpose architectures made out of arithmetic operators or to produce parallel architectures. In both cases, the output may be either efficient special-purpose hardware for computation-intensive tasks and/or the parameters for a reconfigurable architecture. Such approaches will eventually create a bridge between compilation techniques and hardware design.

Finally, we continue to investigate floating-point to fixed-point automatic conversion with the objective to develop an open-source tool. Multimedia and signal processing are main application fields for reconfigurable platforms. In general, these algorithms are specified using floating-point operations, but, for efficiency reasons, they are often implemented with fixed-point operations either in software for DSP cores or as special-purpose hardware. Unfortunately, fixed-point conversion is very challenging and time-consuming, typically demanding 25 to 50% of the total design or implementation time<sup>2</sup>. Thus, tools are required to automate this conversion. In software implementations (DSP, MCU), the aim is to define an optimized fixed-point specification which

<sup>&</sup>lt;sup>2</sup>http://www.mathworks.com/company/newsletters/digest/may04/uwb.html

minimizes the code size and the execution time for a given computation accuracy constraint. This optimization is achieved through the modification of the scaling operation location and the selection of the data word-length according to the different data-types supported by DSPs. In hardware implementations (ASIC, FPGA), the complete architecture has to be defined. The efficient implementation requires to minimize the architecture size and the power consumption. Thus, the conversion process goal is to minimize the operator word-length. In the fixed-point conversion process, one of the main challenge is to evaluate the fixed-point specification accuracy. For DSP-software implementation, methodologies have been proposed [105], [109], [108] to achieve a floating-point to fixed-point conversion leading to an ANSI-C code with integer data types. One of the key is to closely link the compilation flow to the latest DSP features. For hardware implementation, the best results are obtained when the word-length optimization process is coupled with the high-level synthesis [104] [96].

## 3.4. Algorithm Architecture Interaction

As CAIRN mainly targets domain-specific systems-on-chip including reconfigurable capabilities, algorithmic-level optimizations have a great potential on the efficiency of the overall system. Based on the skills and experiences in "signal processing and communications" of some CAIRN's members, we conduct research on algorithmic optimization techniques under two main constraints: energy consumption and computation accuracy; and for two main application domains: fourth-generation (4G) mobile telecommunications and wireless sensor networks (WSN). These application domains are very conducive to our research activities. The high complexity of the first one and the stringent power constraint of the second one, require the design of specific high-performance and energy efficient SoCs. Sections 4.1 to 4.4 detail the application domains that we focus on.

We also work on computer arithmetic operators and representations of numbers for hardware and software implementations. We provide algorithms for evaluating operations such as: addition, multiplication, multiplication by constant, power, division, roots, (inverse) trigonometric functions, (inverse) hyperbolic functions, logarithms, exponentials, and combinations. For hardware implementations, we work on the reduction of the delay, silicon area and power consumption. For software implementations, we focus on high-performance computing libraries on general purpose processors (GPPs) and graphic processor units (GPUs). We work on the use of exotic representations of numbers in specific domains such as secured implementations of cryptosystems with high-performance protection against side-channel analysis or fault attacks.

# 4. Application Domains

#### 4.1. Panorama

Our research is based on realistic applications, in order to both discover the main needs created by these applications and to invent realistic and interesting solutions.

The high complexity of the **Next-Generation (4G) Wireless Communication Systems** leads to the design of real-time high-performance specific architectures. The study of these techniques is one of the main field of applications for our research, based on our experience on WCDMA for 3G implementation.

In **Wireless Sensor Networks** (WSN), where each wireless node has to operate without battery replacement for a long time, energy consumption is the most important constraint. In this domain, we mainly study energy-efficient architectures and wireless cooperative techniques for WSN.

**Intelligent Transportation Systems** (ITS), and especially Automotive Systems, more and more apply technology advances. While wireless transmissions allow a car to communicate with another or even with road infrastructure, **automotive industry** can also propose driver assistance and more secure vehicles thanks to improvements in computation accuracy for embedded systems.

Other important fields will also be considered: hardware cryptographic and security modules, specialized hardware systems for the filtering of the network traffic at high-speed, high-speed true-random number generation for security, content-based image retrieval and video processing.

## 4.2. 4G Wireless Communication Systems

With the advent of the next generation (4G) broadband wireless communications, the combination of MIMO (Multiple-Input Multiple-Output) wireless technology with Multi-Carrier CDMA (MC-CDMA) has been recognized as one of the most promising techniques to support high data rate and high performance. Moreover, future mobile devices will have to propose interoperability between wireless communication standards (4G, WiMax ...) and then implement MIMO pre-coding, already used by WiMax standard. Finally, in order to maximize mobile devices lifetime and guarantee quality of services to consumers, 4G systems will certainly use cooperative MIMO schemes or MIMO relays. Our research activity focuses on MIMO pre-coding and MIMO cooperative communications with the aim of algorithmic optimization and implementation prototyping.

#### 4.3. Wireless Sensor Networks

Sensor networks are a very dynamic domain of research due, on the one hand, to the opportunity to develop innovative applications that are linked to a specific environment, and on the other hand to the challenge of designing totally autonomous communicating objects. Cross-layer optimizations lead to energy-efficient architectures and cooperative techniques dedicated to sensor networks applications. In particular, cooperative MIMO techniques are used to decrease the energy consumption of the communications.

## 4.4. Multimedia processing

In multimedia applications, audio and video processing is the major challenge embedded systems have to face. It is computationally intensive with power requirements to meet. Video or image processing at pixel level, like image filtering, edge detection and pixel correlation or at bloc level such as transforms, quantization, entropy coding and motion estimation have to be accelerated. We investigate the potential of reconfigurable architectures for the design of efficient and flexible accelerators in the context of multimedia applications.

## 5. Software

#### 5.1. Panorama

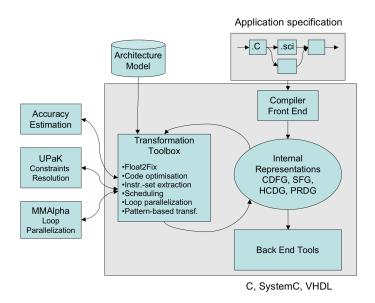

Besides the development of new reconfigurable architectures, the need for efficient compilation flow is stronger than ever. Challenges come from the high parallelism of these architectures and also from new constraints such as resource heterogeneity, memory hierarchy and power constraints and management. We aim at defining a highly effective software framework for the compilation of high-level specifications into optimized code executed on a reconfigurable hardware platform. Figure 2 shows the global framework that we are currently developing.

Our approach assumes that the application is specified as a hierarchical block diagram of communicating tasks expressing data-flow or control, where each task is expressed using languages like C, Signal, Scilab or Matlab, and is then transformed into an internal representation by the compiler front-end. Then, our framework is based on applying some high-level transformations onto the internal representation.

Figure 2. CAIRN's general software development framework

Different internal representations are used depending on the targeted transformations or the targeted architectures.

- The classical Control and Data Flow Graph (CDFG) is the main internal formalism of our framework. It is the basis for transformations like code optimizations, fixed-point transformations, instruction-set extraction or scheduling. Gateways will be provided from CDFG to other supported formalisms.

- The Hierarchical Conditional Dependency Graph (HCDG) format is also used as the internal representation for pattern-based transformations.

- Other internal representations like Signal Flow Graphs (SFG) and Polyhedral Reduced Dependence Graph (PRDG) will be used respectively for application accuracy estimation and loop parallelization techniques.

Finally, back-end tools enable the generation of code like VHDL for the hardwired or reconfigurable blocks, C for embedded processor software, and SystemC for simulation purposes (e.g. fixed-point simulations). The compiler front-end, the back-end generators, the transformation toolbox as well as the different internal representations and their respective gateways are based on a single framework: the Gecos framework.

Besides CAIRN's general design workflow, and in order to promote research undertaken by CAIRN, several hardware and software prototypes are developed. Among those, some distributed software are presented in this report: Gecos a flexible compilation platform, ID.Fix an infrastructure for the automatic transformation of software code aiming at the conversion of floating-point data types into a fixed-point representation, UPaK and Durase for the compilation and the synthesis targeting reconfigurable platforms, and Interconnect Explorer a high-level power and delay estimation tool for on-chip interconnects.

### 5.2. Gecos

**Participants:** Steven Derrien [correspondant], Daniel Menard, Kevin Martin, Maxime Naullet, Antoine Floch, Antoine Morvan, Clément Guy, Amit Kumar.

The Gecos (Generic Compiler Suite) project is an open source Eclipse-based C compiler infrastructure developed in the CAIRN group since 2004 that allows for fast prototyping of complex compiler passes. Gecos was designed so as to address part of the shortcomings of existing C/C++ infrastructures such as SUIF and LLVM

Gecos is a 100% Java based implementation and is based on modern software engineering practices. It uses Eclipse plugin as an underlying infrastructure and thus takes benefits of its plugin mechanism to be easily extensible. Gecos follows Model Driven Software Engineering techniques and rely on Eclipse Modeling Framework. The framework is open-source and is hosted on the INRIA gforge at <a href="http://gecos.gforge.inria.fr">http://gecos.gforge.inria.fr</a>.

The Gecos infrastructure is still under very active development, and now serves as a backbone infrastructure to many group members (Upak, Durase, ID.Fix). In 2011, the work has focused on extending the loop analysis transformation framework, which now includes an OpenMP static analysis tool (developed jointly with Colorado State University) that was presented in June at the 7th International Workshop on OpenMP [39]. The software engineering challenges posed by optimizing compiler also happen to be a novel and promising application field for the MDE community, which led to joint publication [45] with members from CSU and the Triskell EPI team at the IEEE/ACM Models conference in October 2011. This cross fertilization between MDE and Compilers is the core topic of Clément Guy's PhD thesis supervised by members of CAIRN (S. Derrien) and Triskell (J.M. Jezequel and B. Combemale).

## 5.3. ID.Fix: Infrastructure for the Design of Fixed-point Systems

**Participants:** Daniel Menard [correspondant], Olivier Sentieys, Romuald Rocher, Nicolas Simon, Quentin Meunier.

The different techniques proposed by the team for fixed-point conversion are implemented on the ID.Fix infrastructure. The application is described with a C code using floating-point data types and different pragmas, used to specify parameters (dynamic, input/output word-length, delay operations) for the fixed-point conversion. This tool determines and optimizes the fixed-point specification and then, generates a C code using fixed-point data types (ac\_fixed) from Mentor Graphics. The infrastructure is made-up of three main modules corresponding to the fixed-point conversion (Fix.Conv), the accuracy evaluation (Acc.Eval) and the dynamic range evaluation (Dyn.Eval).

The different developments carried-out in 2011 allow obtaining a fixed-point conversion tool handling functions, conditional structures and repetitive structures having a fixed number of iterations during time. For the accuracy evaluation (Acc.Eval), conditional structures and correlation between noise sources have been considered. For the dynamic range evaluation (Dyn.Eval), the method based on the Karhunen-Loève Expansion (KLE) have been implemented. It allows determining the dynamic range for a given overflow probability.

The development of this tool has been achieved thanks to an INRIA post-doc in the context of S2S4HLS project until August 2011, and a University of Rennes graduate engineer from November 2011 in the context of DEFIS ANR project and different students during their training period.

# 5.4. UPaK: Abstract Unified Pattern-Based Synthesis Kernel for Hardware and Software Systems

Participants: Christophe Wolinski [correspondant], François Charot, Antoine Floch.

We are developing (with strong collaboration of Lund University, Sweden and Queensland University, Australia) UPaK Abstract Unified Pattern Based Synthesis Kernel for Hardware and Software Systems [119]. The preliminary experimental results obtained by the UPak system show that the methods employed in the systems enable a high coverage of application graphs with small quantities of patterns. Moreover, high application execution speed-ups are ensured, both for sequential and parallel application execution with processor extensions implementing the selected patterns. UPaK is one of the basis for our research on compilation and synthesis for reconfigurable platforms. It is based on the HCDG representation of the Polychrony software designed at INRIA-Rennes in the project-team Espresso.

# 5.5. DURASE: Automatic Synthesis of Application-Specific Processor Extensions

Participants: Christophe Wolinski [correspondant], François Charot, Antoine Floch.

We are developing a framework enabling the automatic synthesis of application specific processor extensions. It uses advanced technologies, such as algorithms for graph matching and graph merging together with constraints programming methods. The framework is organized around several modules.

- CoSaP: Constraint Satisfaction Problem. The goal of CoSaP is to decouple the statement of a

constraint satisfaction problem from the solver used to solve it. The CoSaP model is an Eclipse

plugin described using EMF to take advantage of the automatic code generation and of various EMF

tools.

- HCDG: Hierarchical Conditional Dependency Graph. HCDG is an intermediate representation

mixing control and data flow in a single acyclic representation. The control flow is represented as

hierarchical guards specifying the execution or the definition conditions of nodes. It can be used in

the Gecos compilation framework via a specific pass which translates a CDFG representation into

an HCDG.

- Patterns: Flexible tools for identification of computational pattern in a graph and graph covering.

These tools model the concept of pattern in a graph and provide generic algorithms for the

identification of pattern and the covering of a graph. The following sub-problems are addressed:

(sub)-graphs isomorphism, patterns generation under constraints, covering of a graph using a library

of patterns. Most of the implemented algorithms use constraints programming and rely on the CoSaP

module to solve the optimization problem.

# **5.6.** PowWow: Power Optimized Hardware and Software FrameWork for Wireless Motes (AP-L-10-01)

**Participants:** Olivier Sentieys [correspondant], Olivier Berder, Romain Fontaine, Arnaud Carer, Samuel Mouget, Steven Derrien.

PowWow is an open-source hardware and software platform designed to handle wireless sensor network (WSN) protocols and related applications. Based on an optimized preamble sampling medium access (MAC) protocol, geographical routing and protothread library, PowWow requires a lighter hardware system than Zigbee [90] to be processed (memory usage including application is less than 10kb). Therefore, network lifetime is increased and price per node is significantly decreased.

CAIRN's hardware platform (see Figure 3) is composed of:

- The motherboard, designed to reduce power consumption of sensor nodes, embeds an MSP430 microcontroller and all needed components to process PowWow protocol except radio chip. JTAG, RS232, and I2C interfaces are available on this board.

- The radio chip daughter board is currently based on a TI CC2420.

- The coprocessing daughter board includes a low-power FPGA which allows for hardware acceleration for some PowWow features and also includes dynamic voltage scaling features to increase power efficiency. The current version of PowWow integrates an Actel IGLOO AGL250 FPGA and a programmable DC-DC converter. We have shown that gains in energy of up to 700 can be obtained by using FPGA acceleration on functions like CRC-32 or error detection with regards to a software implementation on the MSP430.

PowWow distribution also includes a generic software architecture using event-driven programming and organized into protocol layers (PHY, MAC, LINK, NET and APP). The software is based on Contiki [100], and more precisely on the Protothread library which provides a sequential control flow without complex state machines or full multi-threading.

Figure 3. CAIRN's PowWow motherboard with radio board connected

To optimize the network regarding a particular application and to define a global strategy to reduce energy, PowWow offers the following extra tools: over-the-air reprogramming (and soon reconfiguration), analytical power estimation based on software profiling and power measurements, a dedicated network analyzer to probe and fix transmissions errors in the network. More information can be found at <a href="http://powwow.gforge.inria.fr">http://powwow.gforge.inria.fr</a>.

# 5.7. SoCLib: Open Platform for Virtual Prototyping of Multi-Processors System on Chip

Participants: François Charot [correspondant], Laurent Perraudeau, Charles Wagner.

SoCLib is an open platform for virtual prototyping of multi-processors system on chip (MP-SoC) developed in the framework of the SoCLib ANR project. The core of the platform is a library of SystemC simulation models for virtual components (IP cores), with a guaranteed path to silicon. All simulation models are written in SystemC, and can be simulated with the standard SystemC simulation environment distributed by the OSCI organization. Two types of models are available for each IP-core: CABA (Cycle Accurate / Bit Accurate), and TLM-DT (Transaction Level Modeling with Distributed Time). All simulation models are distributed as free software. We have developed the simulation model of the NIOSII processor, of the Altera Avalon interconnect, and of the TMS320C62 DSP processor from Texas Instruments. Find more information on its dedicated web page: http://www.soclib.fr.

## 5.8. OCHRE: On-Chip Randomness Extraction

Participants: Olivier Sentieys [correspondant], Arnaud Carer, Arnaud Tisserand.

Ochre is a set of synthesizable VHDL models for true and pseudo random number generation and hardware accelerated statistical tests. It includes IP cores of different oscillator-based TRNGs, different PRNGs (linear feedback shift registers, cellular automata, AES) and several statistical tests (FIPS 140-2, AIS31, Diehard). This set of IPs has been used to design Ochre V1 and V2 chips and were delivered under license to a company.

## 6. New Results

## 6.1. Dynamically and Heterogeneous Reconfigurable Platforms

#### 6.1.1. New Reconfigurable Architectures

6.1.1.1. Power models of reconfigurable architectures

Participants: Robin Bonamy, Daniel Chillet, Olivier Sentieys.

Including a reconfigurable area in complex systems-on-chip is now considered as an interesting solution to reduce the area of the global system and to support high performances. But the key challenge in the context of embedded systems is currently the power budget of the system, and the designer needs some early estimations of the power consumption of its system. Power estimation for reconfigurable systems is a difficult problem because several parameters need to be taken into account to define an accurate model.

Hardware implementation of an algorithm provides different choices to the designer compared to software implementation. It is possible to vary the parallelism level or loop unrolling index, which has a direct impact on area and execution time and therefore on power and energy consumption. First we evaluated delay, area, power and energy impacts of loop transformations using High Level Synthesis tools. We have made several power measurements on a real FPGA platform and for different task implementations in order to build a model of energy consumption versus execution time. Work is in progress to also characterize energy consumption of tasks through extracting the number of elementary operators used in the hardware implemented task.

Furthermore, we also consider the opportunity of the dynamic reconfiguration, which makes possible to partially reconfigure a specific part of the circuit while the rest of the system is running. This opportunity has two main effects on power consumption. First, thanks to the area sharing ability, the global size of the device can be reduced and the static (leakage) power consumption can thus be reduced. Secondly, it is possible to delete the configuration of a part of the device which reduces the dynamic power consumption when a task is no longer used. Although the cost of the reconfiguration is still important, in some cases this technique can be interesting to reduce the power of the system. To evaluate the potential gain of the dynamic reconfiguration, we have made some measurements on a Virtex 5 board. We have defined a first model of the power consumption of the reconfiguration. This model shows that the power consumption not only depends on the bitstream file size but also on the content of the reconfiguration region [41], [42].

These experiments allow us to define energy and delay models that will be used by the operating system including a power management strategy to decide on-line which task instances must be executed to efficiently manage the available power using dynamic partial reconfiguration [82].

6.1.1.2. High-level modeling of reconfigurable architectures

Participants: Robin Bonamy, Daniel Chillet, Sébastien Pillement.

To help System-on-Chip designers to explore the large design space, high-level methodologies and tools are more and more often required. The exploration phase is particularly difficult when the system must satisfy a large number of constraints, like performance, real time and power consumption. If the classical multiprocessor system-on-chips can be modeled without any difficulty, dynamically reconfigurable embedded accelerators are not correctly covered by the usual modeling languages.

In this context, we have extended the AADL (Architecture Analysis and Design Language) language to include the reconfiguration aspect included in nowadays' MPSoC [19], [40]. This work is part of a more general project, Open-People, which proposes complete methodology for power and energy consumption analysis. The proposal is based on AADL property extensions which are applied on component models. A three-level model has been defined for every targeted FPGA. The first level defines a generic FPGA which allows to model every possible FPGA. The second level allows the specialization of the FPGA for a specific family. Finally, the third level provides the support to describe the deployment of an application on a specific FPGA circuit.

To complete these levels of description, we started the development of techniques for constraint verifications. These developments are based on the OCL language, which allows to extract characteristics on the AADL model, compute mathematical expressions and finally verify mathematical constraints. These verifications have been developed for power and energy consumption, they include static and dynamic power estimation and soon the power consumption during the dynamic reconfiguration process.

#### 6.1.1.3. Reconfiguration controller

Participants: Manh Pham, Daniel Chillet, Sébastien Pillement.

Dynamically reconfigurable architectures, which can offer high performance, are increasingly used in different domains. Unfortunately, lots of applications cannot benefit from this new paradigm due to large timing overhead. Even for partial reconfiguration, modifying a small region of an FPGA takes few *ms*. To cope with this problem we have developed an ultra-fast power-aware reconfiguration controller (UPaRC) to boost the reconfiguration throughput up to 1.433 GB/s. UPaRC can not only enhance the system performance, but also auto-adapt to various performance and consumption conditions. This could enlarge the range of supported applications and can optimize power-timing trade-off of reconfiguration phase for each selected application during run-time. The energy-efficiency of UPaRC over state-of-the-art reconfiguration controllers is up to 45 times more efficient. This work has been accepted for publication in DATE'2012 [56].

### 6.1.2. Management of Dynamically Reconfigurable Systems

#### 6.1.2.1. Spatio-Temporal Scheduling based on Artificial Neural Networks

Participants: Antoine Eiche, Daniel Chillet, Sébastien Pillement, Olivier Sentieys.

Management of task execution on dynamically reconfigurable accelerators is known to be a difficult problem due to the large number of possibilities of task instantiations. The problem to solve can be defined as the "spatio-temporal task scheduling". The problem becomes even more difficult to solve when the solutions must be produced during the execution of the application, i.e. on-line. In this context, new algorithms must be defined and, to solve this problem, we propose to define a neural network based on the Hopfield model.

We are therefore able to address heterogeneous multiprocessor systems and to manage the reconfigurable resources embedded within MPSoC [23]. Our latest works on this topic focused on two different issues. First we demonstrated that neural network structures used for task scheduling can continue to produce valid solutions even if one or several neurons are in fault [70]. This characteristic is very important for present and future technologies for which the fabrication process variability can lead to increase the number of defaults in the circuit. The second focus concerned the optimization of the neural network convergence by using parallel evaluation of neurons. We have shown how to define several neuron packets (from the neural network) that can be evaluated in parallel without modifying the convergence property [44], [76].

#### 6.1.2.2. Flexible Communication OS Service

Participants: Daniel Chillet, Sébastien Pillement, Ludovic Devaux.

In a multiprocessor system, to gain the advantages of parallelism, efficient communication and memory management are highly required. Recent developments in the partial and dynamic reconfigurable computing domain demand better ways to manage simultaneous task execution. But, the requirements are slightly different from the traditional software based systems. In this context, Operating System (OS) services like scheduling, placement, inter-task communication have been developed to make such platforms flexible and self-sufficient. For task communications within flexible architectures, we defined a specific network-on-chip adapted to dynamically and partially reconfigurable resources included into modern SoC. The characterization of the *DRAFT* network was completed and its integration inside reconfigurable systems on chip was realized [14]. We then focused on the run-time communication service [50] and dynamic memory management [49] in reconfigurable System-on-Chips (RSoCs). We first developed a hardware communication block and the communication schemes supported by this new OS service. The originality relies on the implementation of this services directly inside the FPGA. We then demonstrated the requirements and advantages of having a local memory task or a dynamically configurable memory task, in order to improve effectiveness and efficiency of the proposed schemes.

#### 6.1.3. Fault-Tolerant Reconfigurable Architectures

Participants: Sébastien Pillement, Manh Pham, Stanislaw Piestrak.

In terms of complex systems implementation, reconfigurable FPGA circuits are now part of the mainstream thanks to their flexibility, performances and high number of integrated resources. FPGAs enter new fields of applications such as aeronautics, military, automotive or confined control thanks to their ability to be remotely updated. However, these fields of applications correspond to harsh environments (cosmic radiation, ionizing, electromagnetic noise) and with high fault-tolerance requirements. We then propose a complete framework to design reconfigurable architecture supporting fault-tolerance mitigation scheme [58]. The proposed framework allows simulation, validation of mitigation operations, but also to size architecture resources. The physical implementation of the fault-tolerant reconfigurable platform permits to validate the proposed model and the effectiveness of the framework. This implementation shows the potential of dynamically reconfigurable architectures for supporting fault-tolerance in embedded systems. We also worked on new approach in order to include dependability in the DRAFT coarse-grained reconfigurable architecture [37].

#### 6.1.4. Low-Power Architectures

6.1.4.1. Ultra Low-Power Architecture for Control-Oriented Applications in Wireless Sensor Nodes

Participants: Olivier Sentieys, Steven Derrien, Vivek D. Tovinakere, Philippe Quémerais, Romain Fontaine.

This research work aims at developing ultra low-power SoC for wireless sensor nodes, as an alternative to existing approaches based low-power micro-controllers. The proposed approach reduces the power consumption by using a combination of hardware specialization and power gating techniques. In particular, we use the fact that typical WSN applications are generally modeled as a set of small to medium grain tasks that are implemented on low power microcontroller using light weight *thread*-like OS constructs.

Rather than implementing these tasks in software, we instead propose to map each of these tasks to their own specialized hardware structures that we call a *hardware micro-task*. Such hardware task consists of a minimalistic (and customized) data-path controlled by a finite state machine (FSM). By customizing each of these hardware implementations to their corresponding task, we expect to significantly reduce the dynamic power dissipated by the whole system. Besides, to circumvent the increase in static power caused by the possibly numerous hardware tasks implemented in the chip, we also propose to combine our approach with *power gating*, so as to supply power to a hardware task only when it needs to be executed [28].

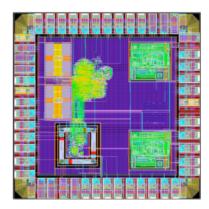

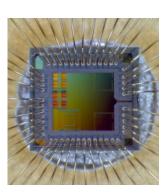

As a prof of concept, a chip has been designed and fabricated in a 65nm CMOS from STMicroelectonics using the CMP facilities. The area is about 1mm<sup>2</sup> in a QFN52 package. The circuit is a controller part of a wireless sensor network node. It embeds an OpenMSP microcontroller core with SRAM memories for data and programs and some dedicated hardware tasks to control an external radio transceiver such as the TI CC2420 commonly used in the industry.

To reduce energy consumption, low power design techniques such as power gating were used. Two power domains are implemented: one is dedicated to microcontroller and memories, while the goal of the second is to measure the efficiency of our hardware micro-task concept.

The input-output ring around the core is divided into three parts: two parts are digital I/O pads corresponding to a power domain and the third contains analog pads to control the power gating for monitoring. Our goal is to analyze the power benefits of our approach and to compare it with classical microprocessor architectures.

6.1.4.2. Wakeup Time and Wakeup Energy Estimation in Power-Gated Logic Clusters

**Participants:** Olivier Sentieys, Vivek D. Tovinakere.

Run-time power gating for aggressive leakage reduction has brought into focus the cost of mode transition overheads due to frequent switching between sleep and active modes of circuit operation. In order to design circuits for effective power gating, logic circuits must be characterized for overheads they present during mode transitions. We have proposed a method to determine steady-state virtual-supply voltage in active mode and hence present a model for virtual-supply voltage in terms of basic circuit parameters. Further, we derived

Figure 4. Layout and Die of Express-Chip Test Chip

expressions for estimation of two mode transition overheads: wakeup time and wakeup energy for a power-gated logic cluster using the proposed model. Experimental results of application of the model to ISCAS85 benchmark circuits show that wakeup time may be estimated within an average error of 16.3% across  $22\times$  variation in sleep transistor sizes and  $13\times$  variation in circuit sizes with significant speedup in computation time compared to SPICE level circuit simulations [30], [63].

#### 6.1.5. Arithmetic Operators for Cryptography

Participants: Arnaud Tisserand, Thomas Chabrier, Danuta Pamula.

#### 6.1.5.1. ECC Processor with Protections Against SCA

A dedicated processor for elliptic curve cryptography (ECC) is under development. Functional units for arithmetic operations in  $\mathbb{F}_{2^m}$  and  $\mathbb{F}_p$  finite fields and 160–600-bit operands have been developed for FPGA implementation. Several protection methods against side channel attacks (SCA) have been studied. The use of some number systems, especially very redundant ones, allows to change the way some computations are performed and then their effects on side channel traces.

We propose in [83] hardware implementation of the double base number system (DBNS) random recoding of secret keys. This recoding is performed on-the-fly during the elliptic curve cryptograpy (ECC) scalar multiplication [k]P. This leads random behavior of the point operations at the side channel level.

We started a collaboration with the University of Sfax in Tunisia on the use of ECC processor for secure communications in low-cost wireless applications. A first FPGA implementation is under development and we expect to submit our first results in 2012.

### 6.1.5.2. Arithmetic Operators for High-Performance Cryptography

In [32], we published an extended version of the work started in 2010 on fast algorithms and implementations of  $\mathbb{F}_{2^m}$  finite field multiplication units in FPGA. The proposed and compared methods are based on separated multiplication and reduction steps and analyzed various area and time dependency/efficiency/complexity tradeoffs.

With Mark Hamilton, PhD student in the Code and Crypto group from the University College Cork (UCC), we worked on fast algorithms and implementations of  $\mathbb{F}_p$  finite field multipliers for some specific values of p. The corresponding results have been published in [46].

#### 6.1.6. SoC Modeling and Prototyping on FPGA-based Systems

Participants: François Charot, Kevin Martin, Laurent Perraudeau, Charles Wagner.

SoCLib and MutekH are two software development projects to which we contribute. SoCLib (http://www.soclib.fr) is an open platform for modeling and simulation of multiprocessors system-on-chip (MP-SoC). MutekH (http://www.mutekh.org) is a free and portable operating system for embedded platforms, ranging from micro-controller to multiprocessor systems. The use of the configurable and extensible simulation model of the Altera NIOSII processor of the SoCLib library and of the MutekH operating system allows us to easily deploy software applications such as codes from MediaBench, MiBench and Cryptographic Library benchmark sets or multithreaded applications on monoprocessor and multiprocessor simulation platforms. These platforms are used on the one hand for the validation of the processor extensions automatically generated by our compilation tools and on the other hand for the measurement of the speedup achieved using these new extensions.

## **6.2.** Compilation and Synthesis for Reconfigurable Platform

**Participants:** Steven Derrien, Emmanuel Casseau, Daniel Menard, François Charot, Christophe Wolinski, Olivier Sentieys, Patrice Quinton.

#### 6.2.1. Polyhedral based loop transformations for High-Level synthesis

Participants: Steven Derrien, Antoine Morvan, Patrice Quinton.

After almost two decades of research effort, there now exists a large choice of robust and mature C to hardware tools that are used as production tools by world-class chip vendor companies. Although these tools dramatically slash design time, their ability to generate efficient accelerators is still limited, and they rely on the designer to expose parallelism and to use appropriate data layout in the source program. We believe this can be overcome by tackling the problem directly at the source level, using source-to-source optimizing compilers. More precisely, our aim is to study how polyhedral based program analysis and transformation can be used to address this problem.

In the context of the PhD of Antoine Morvan, we have studied how it was possible to improve the efficiency and applicability of nested loop pipelining (also known as nested software pipelining) in C to hardware tools. Loop pipelining is a key transformation in high-level synthesis tools as it helps maximizing both computational throughput and hardware utilization. Nevertheless, it somewhat looses its efficiency when dealing with small trip-count inner loops, as the pipeline latency overhead quickly limits its efficiency.

Even if it is possible to overcome this limitation by pipelining the execution of a whole loop nest, the applicability of nested loop pipelining has so far been limited to a very narrow subset of loops, namely perfectly nested loops with constant bounds. In this work, we have extended the applicability of nested-loop pipelining to imperfectly nested loops with affine dependencies. We have shown how such loop nest can be analyzed and, under certain conditions, how one can modify the source code in order to allow nested loop pipeline to be applied using a method called polyhedral bubble insertion. Our approach shown encouraging results and led to a publication to the IEEE International Conference on Field Programmable Technology [48] in December 2011.

#### 6.2.2. Reconfigurable Processor Extensions Generation

Participants: Christophe Wolinski, François Charot, Erwan Raffin, Kevin Martin, Antoine Floch.

During this year, we have continued our work on the generation of reconfigurable processor extension using the constraint programming approach. Previously, we showed how all the problems ranging from instruction identification, scheduling and binding to optimized architecture synthesis can be defined and solved using the constraint programming approach. This year, a new pattern scheduling approach has been defined. It enables concurrent match selection and parallel match scheduling on the processor and extension assuming that the execution on an extension is not atomic. It means that the data produced by an extension must not necessarily be sent to the processor just after the end of processing. Thanks to that, a better scheduling can be obtained [71]. The efficient FPGA implementation of processing units require optimization of hardware resources, such as registers and multiplexers. The extension synthesis defined previously has been revisited. For applications from MediaBench, MiBench and MiCrypt benchmark sets, an improvement of 35%, after placement and routing on the Stratix2 Altera FPGA, is observed.

#### 6.2.3. Run-time Reconfigurable Architecture Modeling

Participants: Christophe Wolinski, François Charot, Emmanuel Casseau, Daniel Menard, Antoine Floch, Erwan Raffin, Steven Derrien.

We have continued to work on the modeling problem of the run-time reconfigurable, operator-based, ROMA multimedia architecture. The ROMA processor is composed of a set of M coarse-grained reconfigurable operators, N data memories, a configuration memory, two interconnection networks (between operators and between operators and memories), and dedicated controllers designed for each module of the datapath. A centralized controller manages the configuration and the execution steps. The ROMA processor has three different interfaces: a data interface connected to the operator network, a control interface and a debug interface connected to the main controller. The number of operators, the number of memories and their size can be decided according to application requirements. The compilation flow of our framework rests on the use of an architecture abstract model of the targeted ROMA architecture.

During this year we have focused on the definition of the constraint model to deploy an application graph on the pipeline architecture model. The goal is here to minimize the latency of the pipeline. The main changes are at the operator and memory levels. The operators are pipelined and the dual port memories behave like circular buffers. Recall that in the case of the non pipelined model, the goal is to optimize the execution time of the application under resource constraints. We have carried out experiments to evaluate the quality of our method using different pattern libraries (patterns supported by the ROMA SWP coarse-grained reconfigurable operator, patterns extracted from the MediaBench set) [47]. In these experiments the model has no limitation in terms of number of operators and number of memories. The optimality of the solutions were proven in 93% of cases. More details can be found in [29] and in the Ph.D. thesis of Erwan Raffin [17].

In the context of the *RecMotifs* project, we have continued to work on a specific design flow integrating STMicroelectronics' compiler flow. This project also allowed us to bring significant evolution to our pattern analysis software tools. The RecMotifs flow consists in a pattern analysis flow for STMicroelectronics *graphml* files generated by ST compiler. This flow allows pattern description (description of *graphml* pattern that can be used in the covering pass), type extraction, pattern generation (pattern generation on a *graphml* file), covering (covering of a *graphml* file with minimization of the parallel execution time without any resource constraints). Once the pattern analysis has been applied to the *graphml* files, C code regeneration can be performed using GeCos.

#### 6.2.4. Floating-Point to Fixed-Point Conversion

Participants: Daniel Menard, Karthick Parashar, Olivier Sentieys, Romuald Rocher, Hai-Nam Nguyen.

For the fixed-point conversion process, different optimization algorithms have been tested. The aim is to minimize the implementation cost under accuracy constraint. In [54], two new algorithms for the word-length optimization procedure, based on the Greedy Randomized Adaptive Search Procedure (GRASP), are proposed. Compared to existing methods, our proposition yields better results and has a complexity between deterministic methods and stochastic methods.

#### 6.3. Algorithm Architecture Interaction

### 6.3.1. Flexible hardware accelerators for biocomputing applications

Participants: Steven Derrien, Naeem Abbas, Patrice Quinton.

It is widely acknowledged that FPGA-based hardware acceleration of compute intensive bioinformatics applications can be a viable alternative to cluster (or grid) based approach as they offer very interesting MIPS/watt figure of merits. One of the issues with this technology is that it remains somewhat difficult to use and to maintain (one is rather designing a circuit rather than programming a machine).

Even though there exists C-to-hardware compilation tools (Catapult-C, Impulse-C, etc.), a common belief is that they do not generally offer good enough performance to justify the use of such reconfigurable technology. As a matter of fact, successful hardware implementations of bio-computing algorithms are manually designed at RTL level and are usually targeted to a specific system, with little if any performance portability among reconfigurable platforms.

This research work, which is part of the ANR BioWic project, aims at providing a framework for helping semi-automatic generation of high-performance hardware accelerators. In particular we expect to widen the scope of common design constraints by focusing on system-level criterions that involve both the host machine and the accelerator (workload balancing, communications and data reuse optimisations, hardware utilization rate, etc.). This research work builds upon the CAIRN research group expertise on automatic parallelization for application specific hardware accelerators and has been targeting mainstream bioinformatics applications (HMMER, ClustalW and BLAST).

Our work in 2011 extended the experiment results obtained in 2010 and led to the submission of a paper to IEEE Trans. in Parallel and Distributed Computing (the article being in revision). We also investigated another case study based on a more classical sequence comparison algorithm for which we investigated different style of architectural partitioning. This work led to a paper published in the proceedings of the ARC International Symposium [43].

#### 6.3.2. Range Estimation and Computation Accuracy Optimization

**Participants:** Daniel Menard, Karthick Parashar, Olivier Sentieys, Romuald Rocher, Pascal Scalart, Aymen Chakhari, Jean-Charles Naud, Emmanuel Casseau, Andrei Banciu.

#### 6.3.2.1. Range Estimation

Efficient range estimation methods are required to optimize the integer part word-length. Our previous works based on the Karhunen-Loève Expansion (KLE) have been extended in [38]. The impulse response between the input and a variable is used to propagate the KLE parameters of the inputs. Range estimation has proven to be a difficult problem for non-linear operations especially when the input data is correlated. A stochastic approach can significantly improve the results compared to the classical methods like the interval and affine arithmetic. The aim is to obtain tight intervals by adapting the bounds to a desired probability of overflows. An approach for the analysis of range uncertainties based on the Polynomial Chaos Expansion (PCE) has been developed. The PCE representation is obtained for every input variable and an analytical description of the variability of the output is determined. Furthermore, the correlation of the inputs is captured using the Nataf transform. The range is computed using a probabilistic analysis from the probability density function (PDF).

#### 6.3.2.2. Accuracy and performance evaluation