# **Activity Report 2016**

# **Project-Team PACAP**

# Pushing Architecture and Compilation for Application Performance

IN COLLABORATION WITH: Institut de recherche en informatique et systèmes aléatoires (IRISA)

RESEARCH CENTER

Rennes - Bretagne-Atlantique

**THEME**

**Architecture, Languages and Compilation**

# **Table of contents**

| 1.        | Members                                                                                                                                                                                                                    |                            |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 2.        | Overall Objectives                                                                                                                                                                                                         | 2                          |

|           | 2.1.1. Long-Term Goal                                                                                                                                                                                                      | 2                          |

|           | 2.1.2. Approach                                                                                                                                                                                                            | 3                          |

|           | 2.1.3. Latency-oriented Computing                                                                                                                                                                                          | 3                          |

|           | 2.1.4. Throughput-Oriented Computing                                                                                                                                                                                       | 3                          |

|           | 2.1.5. Real-Time Systems – WCET                                                                                                                                                                                            | 3                          |

|           | 2.1.6. Performance Assessment                                                                                                                                                                                              | 4                          |

|           | 2.1.7. Dealing with Faults – Reliability                                                                                                                                                                                   | 4                          |

|           | 2.1.8. Dealing with Attacks – Security                                                                                                                                                                                     | 5                          |

|           | 2.1.9. Green Computing                                                                                                                                                                                                     | 5                          |

| <b>3.</b> | Research Program                                                                                                                                                                                                           | 5                          |

|           | 3.1. Motivation                                                                                                                                                                                                            | 5                          |

|           | 3.1.1. Technological constraints                                                                                                                                                                                           | 5                          |

|           | 3.1.2. Evolving community                                                                                                                                                                                                  | 6                          |

|           | 3.1.3. Domain constraints                                                                                                                                                                                                  | 6                          |

|           | 3.2. Research Objectives                                                                                                                                                                                                   | 6                          |

|           | 3.2.1. Static Compilation                                                                                                                                                                                                  | 7                          |

|           | 3.2.2. Software Adaptation                                                                                                                                                                                                 | 7                          |

|           | 3.2.3. Research directions in uniprocessor microarchitecture                                                                                                                                                               | 8                          |

|           | 3.2.4. Towards heterogeneous single-ISA CPU-GPU architectures                                                                                                                                                              | 9                          |

|           | 3.2.5. Real-time systems                                                                                                                                                                                                   | 10                         |

|           | 3.2.6. Fault Tolerance                                                                                                                                                                                                     | 10                         |

|           | 3.2.7. Power efficiency                                                                                                                                                                                                    | 11                         |

|           | 3.2.8. Security                                                                                                                                                                                                            | 12                         |

| 4.        | Application Domains                                                                                                                                                                                                        | 13                         |

| 5.        | Highlights of the Year                                                                                                                                                                                                     | 13                         |

| 6.        | New Software and Platforms                                                                                                                                                                                                 | 14                         |

|           | 6.1. ATMI                                                                                                                                                                                                                  | 14                         |

|           | 6.2. Heptane                                                                                                                                                                                                               | 14                         |

|           | 6.3. Tiptop                                                                                                                                                                                                                | 15                         |

|           | 6.4. ATC                                                                                                                                                                                                                   | 15                         |

|           | 6.5. Barra                                                                                                                                                                                                                 | 16                         |

|           | 6.6. If-memo                                                                                                                                                                                                               | 16                         |

|           | 6.7. Padrone                                                                                                                                                                                                               | 16                         |

|           | 6.8. STiMuL                                                                                                                                                                                                                | 17                         |

|           | 6.9. TPCalc                                                                                                                                                                                                                | 17                         |

|           | 6.10. Parasuite                                                                                                                                                                                                            | 17                         |

|           | 6.11. Simty                                                                                                                                                                                                                | 18                         |

| 7.        | New Results                                                                                                                                                                                                                | 18                         |

|           | 7.1. Compiler, vectorization, interpretation                                                                                                                                                                               | 18                         |

|           |                                                                                                                                                                                                                            | 10                         |

|           | 7.1.1. Improving sequential performance through memoization                                                                                                                                                                | 18                         |

|           | <ul><li>7.1.1. Improving sequential performance through memoization</li><li>7.1.2. Optimization in the Presence of NVRAM</li></ul>                                                                                         |                            |

|           |                                                                                                                                                                                                                            | 18                         |

|           | 7.1.2. Optimization in the Presence of NVRAM                                                                                                                                                                               | 18<br>19<br>19             |

|           | <ul><li>7.1.2. Optimization in the Presence of NVRAM</li><li>7.1.3. Hardware/Software JIT Compiler</li></ul>                                                                                                               | 18<br>19                   |

|           | <ul> <li>7.1.2. Optimization in the Presence of NVRAM</li> <li>7.1.3. Hardware/Software JIT Compiler</li> <li>7.1.4. Dynamic Parallelization of Binary Programs</li> </ul>                                                 | 18<br>19<br>19<br>19       |

|           | <ul> <li>7.1.2. Optimization in the Presence of NVRAM</li> <li>7.1.3. Hardware/Software JIT Compiler</li> <li>7.1.4. Dynamic Parallelization of Binary Programs</li> <li>7.1.5. Dynamic Function Specialization</li> </ul> | 18<br>19<br>19<br>19<br>20 |

|    | 7.1.9. SPMD Function Call Fusion                                                                      | 21 |

|----|-------------------------------------------------------------------------------------------------------|----|

|    | 7.1.10. SIMD programming in SPMD: application to multi-precision computations                         | 21 |

|    | 7.2. Processor Architecture                                                                           | 21 |

|    | 7.2.1. Microarchitecture                                                                              | 22 |

|    | 7.2.1.1. Branch prediction                                                                            | 22 |

|    | 7.2.1.2. Revisiting Value Prediction                                                                  | 22 |

|    | 7.2.1.3. Physical register sharing                                                                    | 22 |

|    | 7.2.1.4. Register Sharing for Equality Prediction                                                     | 23 |

|    | 7.2.1.5. Storage-Free Memory Dependency Prediction                                                    | 23 |

|    | 7.2.1.6. Compressed Caches                                                                            | 23 |

|    | 7.2.1.7. Clustered microarchitecture                                                                  | 24 |

|    | 7.2.1.8. Hardware data prefetching                                                                    | 24 |

|    | 7.2.1.9. Exploiting loops for lower energy consumption                                                | 24 |

|    | 7.2.2. Microarchitecture Performance Modeling                                                         | 25 |

|    | 7.2.2.1. Optimal cache replacement                                                                    | 25 |

|    | 7.2.2.2. Adaptive Intelligent Memory Systems                                                          | 25 |

|    | 7.2.2.3. Augmenting superscalar architecture for efficient many-thread parallel execution             | 25 |

|    | 7.2.2.4. Generalizing the SIMT execution model to general-purpose instruction sets                    | 26 |

|    | 7.3. WCET estimation and optimization                                                                 | 26 |

|    | 7.3.1. WCET estimation for many core processors                                                       | 26 |

|    | 7.3.1.1. Optimization of WCETs by considering the effects of local caches                             | 26 |

|    | 7.3.1.2. Accounting for shared resource contentions to minimize WCETs                                 | 27 |

|    | 7.3.2. Cache-Persistence-Aware Response-Time Analysis for Fixed-Priority Preemptive System            |    |

|    | 7.3.2. Cuche l'elsistènee l'imaie l'esponse l'ime l'inalysis foi l'ixed l'itority l'écomptive dyster. | 27 |

|    | 7.4. Fault Tolerance                                                                                  | 27 |

| 8. | Bilateral Contracts and Grants with Industry                                                          |    |

| •  | 8.1. Bilateral Contracts with Industry                                                                | 28 |

|    | 8.2. Bilateral Grants with Industry                                                                   | 28 |

|    | 8.2.1. Intel research grant INTEL2014-8957                                                            | 28 |

|    | 8.2.2. Intel research grant INTEL2016-11174                                                           | 28 |

| 9. | Partnerships and Cooperations                                                                         |    |

|    | 9.1. National Initiatives                                                                             | 28 |

|    | 9.1.1. Capacités: Projet "Investissement d'Avenir", 1/11/14 to 31/01/2018                             | 28 |

|    | 9.1.2. Multicore: Inria Project Lab, 2013-2016                                                        | 29 |

|    | 9.1.3. ANR Continuum 2015–2019                                                                        | 29 |

|    | 9.1.4. ANR CHIST-ERA SECODE 2016-2018                                                                 | 29 |

|    | 9.1.5. ANR W-SEPT 2012-2016                                                                           | 29 |

|    | 9.1.6. PEPS INS2I gDGA                                                                                | 29 |

|    | 9.2. European Initiatives                                                                             | 30 |

|    | 9.2.1. FP7 & H2020 Projects                                                                           | 30 |

|    | 9.2.1.1. ANTAREX                                                                                      | 30 |

|    | 9.2.1.2. Eurolab-4-HPC                                                                                | 31 |

|    | 9.2.1.3. DAL                                                                                          | 31 |

|    | 9.2.1.4. ARGO                                                                                         | 32 |

|    | 9.2.2. Collaborations in European Programs, Except FP7 & H2020                                        | 33 |

|    | 9.2.3. Collaborations with Major European Organizations                                               | 33 |

|    | 9.3. International Initiatives                                                                        | 33 |

|    | 9.3.1. PHC IMHOTEP                                                                                    | 33 |

|    | 9.3.2. Inria Associate Teams Not Involved in an Inria International Labs                              | 34 |

|    | 9.3.3. Inria International Partners                                                                   | 34 |

|    | 9.4. International Research Visitors                                                                  | 34 |

|    |                                                                                                       |    |

| 10. Dissemination                                     |    |

|-------------------------------------------------------|----|

| 10.1. Promoting Scientific Activities                 | 34 |

| 10.1.1. Scientific Events Organisation                | 34 |

| 10.1.2. Scientific Events Selection                   | 35 |

| 10.1.2.1. Chair of Conference Program Committees      | 35 |

| 10.1.2.2. Member of the Conference Program Committees | 35 |

| 10.1.3. Journal                                       | 35 |

| 10.1.4. Invited Talks                                 | 35 |

| 10.1.5. Scientific Expertise                          | 35 |

| 10.1.6. Research Administration                       | 35 |

| 10.2. Teaching - Supervision - Juries                 | 36 |

| 10.2.1. Teaching                                      | 36 |

| 10.2.2. Supervision                                   | 36 |

| 10.2.3. Juries                                        | 36 |

| 10.2.3.1. Assistant professor hiring committees       | 37 |

| 10.2.3.2. Professor hiring committee:                 | 37 |

| 10.3. Popularization                                  | 37 |

| 11. Bibliography                                      | 37 |

Creation of the Project-Team: 2016 July 01

# **Keywords:**

# **Computer Science and Digital Science:**

- 1.1. Architectures

- 1.1.1. Multicore

- 1.1.2. Hardware accelerators (GPGPU, FPGA, etc.)

- 1.1.3. Memory models

- 1.1.4. High performance computing

- 1.1.5. Exascale

- 1.1.9. Fault tolerant systems

- 1.1.10. Reconfigurable architectures

- 1.6. Green Computing

- 2.2. Compilation

- 2.2.1. Static analysis

- 2.2.2. Memory models

- 2.2.3. Run-time systems

- 2.2.4. Parallel architectures

- 2.2.5. GPGPU, FPGA, etc.

- 2.2.6. Adaptive compilation

- 2.3.1. Embedded systems

- 2.3.3. Real-time systems

- 4.2. Correcting codes

- 4.4. Security of equipment and software

- 7.11. Performance evaluation

- 7.12. Computer arithmetic

# Other Research Topics and Application Domains:

- 1. Life sciences

- 2. Health

- 3. Environment and planet

- 4. Energy

- 5. Industry of the future

- 6. IT and telecom

- 7. Transport and logistics

- 8. Smart Cities and Territories

- 9. Society and Knowledge

# 1. Members

#### **Research Scientists**

Erven Rohou [Team leader, Inria, Senior Researcher, HDR]

Sylvain Collange [Inria, Researcher]

Pierre Michaud [Inria, Researcher]

André Seznec [Inria, Senior Researcher, HDR]

#### **Faculty Members**

Damien Hardy [Univ. Rennes I, Associate Professor] Isabelle Puaut [Univ. Rennes I, Professor, HDR]

#### Engineers

Nicolas Kiss [Inria, from Apr 2016]

Imane Lasri [Inria, from Mar 2016]

Sébastien Martinez [Univ. Rennes I, from June 2016]

Arthur Perais [Inria]

Emmanuel Riou [Inria, until Nov 2016]

#### **PhD Students**

Arif Ali Ana-Pparakkal [Inria]

Rabab Bouziane [Inria]

Nabil Hallou [Inria, until Nov 2016]

Kleovoulos Kalaitzidis [Inria, from Jun 2016]

Sajith Kalathingal [Inria, until Oct 2016]

Andrea Mondelli [Inria]

Viet Anh Nguyen [Univ. Rennes I]

Benjamin Rouxel [Univ. Rennes I]

Aswinkumar Sridharan [Inria]

Arjun Suresh [Inria, until Jul 2016]

#### **Post-Doctoral Fellows**

Fernando Endo [Inria]

Biswabandan Panda [Inria]

### **Visiting Scientists**

Stefano Cherubin [Politecnico di Milano, from Sep 2016 until Oct 2016]

Anita Tino [Ryerson University, from Oct 2016]

Rubens Emilio Alves Moreira [Universidade Federal de Minas Gerais, from Feb 2016 to May 2016]

#### **Administrative Assistant**

Virginie Desroches [Inria]

# 2. Overall Objectives

# 2.1. Overall Objectives

# 2.1.1. Long-Term Goal

In brief, the long-term goal of the PACAP project-team is about *performance*, that is: how fast programs run. We intend to contribute to the ongoing race for exponentially increasing performance and for performance guarantees.

Traditionally, the term "performance" is understood as "how much time is needed to complete execution". Latency-oriented techniques focus on minimizing the average-case execution time (ACET). We are also interested in other definitions of performance. Throughput-oriented techniques are interested in how many units of computations can be completed per unit of time. This is more relevant on manycores and GPUs where many computing nodes are available, and latency is less critical. Finally, we also study worst-case execution times (WCET). They are extremely important for critical real-time systems where designers must guarantee that deadlines are met, in any situation.

Given the complexity of current systems, simply assessing their performance has become a non-trivial task which we also plan to tackle.

We occasionally consider other metrics related to performance, such as power efficiency, total energy, overall complexity, and real-time response guarantee. Our ultimate goal is to propose solutions that make computing systems more efficient, taking into account current and envisioned applications, compilers, runtimes, operating systems, and microarchitectures. And since increased performance often comes at the expense of another metric, identifying the related trade-offs is of interest to PACAP.

ALF witnessed the end of the "magically" increasing clock frequency and the introduction of commodity multicore processors. PACAP will likely experience the end of Moore's law <sup>1</sup>, and the generalization of commodity heterogeneous manycore processors. This impacts how performance is increased and how it can be guaranteed. It is also a time where exogenous parameters should be promoted to first-class citizens:

- 1. the existence of faults, whose impact is becoming increasingly important when the photo-lithography feature size decreases;

- 2. the need for security at all levels of computing systems;

- 3. green computing, or the growing concern of power consumption.

# 2.1.2. Approach

We strive to address performance in a way as transparent as possible for users. For example, instead of proposing any new language, we consider existing applications (written for example in standard C), and we develop compiler optimizations that immediately benefit programmers; we propose microarchitectural features as opposed to changes in processor instruction sets; we analyze and re-optimize binary programs automatically, without any user intervention.

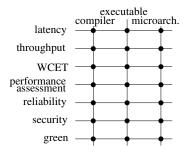

The perimeter of research directions proposed for the PACAP project-team derive from the intersection of two axes: on the one hand, our high-level research objectives, derived from the overall panorama of computing systems, on the other hand the existing expertise and background of the team members on key technology (see illustration on Figure 1). Note that it does not imply that we will systematically explore all intersecting points of the figure, yet all correspond to a sensible research direction. These lists are neither exhaustive, nor final. Operating systems in particular constitute a promising operating point for several of the issues we plan to tackle. Other aspects will likely emerge during the lifespan of the project-team.

# 2.1.3. Latency-oriented Computing

Improving the ACET of general purpose systems has been the core "business" of CAPS and ALF for two decades. We plan to pursue this line of research, acting at all levels: compilation, dynamic optimizations, and microarchitecture.

#### 2.1.4. Throughput-Oriented Computing

The goal is to maximize the performance-to-power ratio. We will leverage the execution model of throughput-oriented architectures (such as GPUs) and extend it towards general purpose systems. To address the memory wall issue, we will consider bandwidth saving techniques, such as cache and memory compression.

#### 2.1.5. Real-Time Systems – WCET

Designers of real-time systems must provide an upper bound of the worst-case execution time of the tasks within their systems. By definition this bound must be safe (i.e. greater than any possible execution time). To be useful, WCET estimates have to be as tight as possible. The process of obtaining a WCET bound consists in analyzing a binary executable, modeling the hardware, and then maximizing an objective function that takes into account all possible flows of execution and their respective execution times. Our research will consider the following directions:

<sup>&</sup>lt;sup>1</sup>Moore's law states that the number of transistors in a circuit doubles (approximately) every two years.

Figure 1. Perimeter of Research Objectives

- 1. better modeling of hardware to either improve tightness, or handle more complex hardware (e.g. multicores);

- 2. eliminate unfeasible paths from the analysis;

- 3. consider probabilistic approaches where WCET estimates are provided with a confidence level.

### 2.1.6. Performance Assessment

Moore's law drives the complexity of processor micro-architectures, which impacts all other layers: hypervisors, operating systems, compilers and applications follow similar trends. While a small category of experts is able to comprehend (parts of) the behavior of the system, the vast majority of users are only exposed to – and interested in – the bottom line: how fast their applications are actually running. In the presence of virtual machines and cloud computing, multi-programmed workload add yet another degree of non-determinism to the measure of performance. We plan to research how application performance can be characterized and presented to a final user: behavior of the microarchitecture, relevant metrics, possibly visual rendering. Targeting our own community, we also research techniques appropriate for fast and accurate ways to simulate future architectures, including heterogeneous designs, such as latency/throughput platforms.

Once diagnosed, the way bottlenecks are addressed depends on the level of expertise of users. Experts can typically be left with a diagnostic as they probably know better how to fix the issue. Less knowledgeable users must be guided to a better solution. We plan to rely on iterative compilation to generate multiple versions of critical code regions, to be used in various runtime conditions. To avoid the code bloat resulting from multiversioning, we will leverage split-compilation to embed code generation "recipes" to be applied just-in-time, or even at rutime thanks to dynamic binary translation. Finally, we will explore the applicability of auto-tuning, where programmers expose which parameters of their code can be modified to generate alternate versions of the program (for example trading energy consumption for quality of service) and let a global orchestrator make decisions.

# 2.1.7. Dealing with Faults - Reliability

Semiconductor technology evolution suggests that permanent failure rates will increase dramatically with scaling. While well-known approaches, such as error correcting codes, exist to recover from failures and provide fault-free chips, the exponential growth of the number of faults will make them unaffordable in the future. Consequently, other approaches like fine-grained disabling and reconfiguration of hardware elements (e.g. individual functional units or cache blocks) will become economically necessary. This fine-grained disabling will degrade performance compared to a fault-free execution. This evolution impacts performance (both ACET and WCET). We plan to address this evolution, and propose new techniques, which can be developed at any level. For example, at microarchitecture level, one might consider designing part of a cache in an older technology to guarantee a minimum level of performance; at compile-time, one might generate

redundant code for critical sections; at run-time, one can monitor faults and apply corrective measures to the software, or hardware. Solutions involving multiple levels are also very promising.

# 2.1.8. Dealing with Attacks - Security

Computer systems are under constant attack, from young hackers trying to show their skills, to "professional" criminals stealing credit card information, and even government agencies with virtually unlimited resources. A vast amount of techniques have been proposed in the literature to circumvent attacks. Many of them cause significant slowdowns due to additional checks and countermeasures. Thanks to our expertise in microarchitecture and compilation techniques, we will be able to significantly improve efficiency, robustness and coverage of security mechanism, as well as to partner with field experts to design innovative solutions.

# 2.1.9. Green Computing

Power consumption has become a major concern of computing systems, at all form factors, ranging from energy-scavenging sensors for IoT, to battery powered embedded systems and laptops, and up to supercomputers operating in the tens of megawatts. Execution time and energy are often related optimization goals. Optimizing for performance under a given power cap, however, introduces new challenges. It also turns out that technologists introduce new solutions (e.g. magnetic RAM) which, in turn, result in new trade-offs and optimization opportunities.

# 3. Research Program

### 3.1. Motivation

Our research program is naturally driven by the evolution of our ecosystem. Relevant recent changes can be classified in the following categories: technological constraints, evolving community, and domain constraints. We hereby summarize these evolutions.

# 3.1.1. Technological constraints

Until recently, binary compatibility guaranteed portability of programs, while increased clock frequency and improved micro-architecture provided increased performance. However, in the last decade, advances in technology and micro-architecture started translating into more parallelism instead. Technology roadmaps even predict the feasibility of thousands of cores on a chip by 2020. Hundreds are already commercially available. Since the vast majority of applications are still sequential, or contain significant sequential sections, such a trend put an end to the automatic performance improvement enjoyed by developers and users. Many research groups consequently focused on parallel architectures and compiling for parallelism.

The focus of ALF – and the DAL ERC – was paradoxically on Amdahl's law: the performance of applications will ultimately be driven by the performance of the sequential part. Despite a number of advances (some of them contributed by ALF), sequential tasks are still a major performance bottleneck. Addressing it is still on the agenda of the proposed PACAP project-team.

In addition, due to power constraints, only part of the billions of transistors of a microprocessor can be operated at any given time (the *dark silicon* paradigm). A sensible approach consists in specializing parts of the silicon area to provide dedicated accelerators (not run simultaneously). This results in diverse and heterogeneous processor cores. Application and compiler designers are now confronted with a moving target, challenging portability and jeopardizing performance.

Finally, we live in a world where billions of sensors, actuators, and computers play a crucial role in our life: flight control, nuclear plant management, defense systems, banking, or health care. These systems must be reliable, despite the fact that they are subject to faults (for example due to aging, charged particle hit, or random noise). Faults will soon become the new *de facto* standard. The evolutions of the semiconductor industry predict an exponential growth of the number of permanent faults [58]. Reliability considerations usually degrade performance. We will propose solutions to mitigate this impact (for example by limiting overheads to critical sections).

Note on technology.

Technology also progresses at a fast pace. We do not propose to pursue any research on technology *per se*. Recently proposed paradigms (quantum computing, non-Si, brain-inspired) have received lots of attention from the research community. We do *not* intend to invest in those paradigms, but we will continue to investigate compilation and architecture for more conventional programming paradigms. Still, several technological shifts may have consequences for us, and we will closely monitor their developments, they include for example non-volatile memory (impacts security, makes writes longer than loads), 3D-stacking (impacts bandwidth), and photonics (impacts latencies and connection network).

## 3.1.2. Evolving community

The PACAP project-team will tackle performance-related issues, for conventional programming paradigms. In fact, programming complex environments is no longer reserved to experts in compilation and architecture. A large community now develops applications for a wide range of targets, including mobile "apps", cloud, multicore or heterogeneous processors.

This also includes domain scientists (in biology, medicine, but also social sciences) who started relying heavily on computational resources, gathering huge amounts of data, and requiring considerable amount of processing to analyze them. Our research is motivated by the growing discrepancy between on the one hand the complexity of the workloads and the computing systems, and on the other hand the expanding community of developers at large, with limited expertise to optimize and to map efficiently computations to compute nodes.

#### 3.1.3. Domain constraints

Mobile, embedded systems have become ubiquitous. Many of them have real-time constraints. For this class of systems, correctness implies not only producing the correct result, but also doing so within specified deadlines. In the presence of heterogeneous, complex and highly dynamic systems, producing *tight* (i.e. useful) upper bound to the worst-case execution time has become extremely challenging. Our research will aim at improving the tightness as well as enlarging the set of features that can be safely analyzed.

The ever growing dependence of our economy on computing systems also implies that security has become of utmost importance. Many systems are under constant attacks from intruders. Protection has a cost also in terms of performance. We plan to leverage our background to contribute solutions that minimize this impact.

Note on Applications Domains.

As was already the case for ALF, PACAP will work on fundamental technologies for computer science: processor architecture, performance-oriented compilation and guaranteed response time for real-time. The research results may have impacts on any application domain that requires high performance execution (telecommunication, multimedia, biology, health, engineering, environment...), but also on many embedded applications that exhibit other constraints such as power consumption, code size and guaranteed response time.

We strive to extract from active domains the fundamental characteristics that are relevant to our research. For example, *big data* is of interest to PACAP because it relates to the study of hardware/software mechanisms to efficiently transfer huge amounts of data to the computing nodes. Similarly, the *Internet of Things* is of interest because it has implications in terms of ultra low power consumption.

# 3.2. Research Objectives

Processor micro-architecture and compilation have been at the core of the research carried by the CAPS and ALF project teams for two decades, with undeniable contributions. They will continue to be the foundation of PACAP.

Heterogeneity and diversity of processor architectures now require new techniques to guarantee that the hardware is satisfactorily exploited by the software. We will devise new static compilation techniques (cf. Section 3.2.1), but also build upon iterative [1] and split [2] compilation to continuously adapt software to its environment (Section 3.2.2). Dynamic binary optimization will also play a key role in delivering adapting software and delivering performance.

The end of Moore's law and Dennard's scaling <sup>2</sup> offer an exciting window of opportunity, where performance improvements will no longer derive from additional transistor budget or increased clock frequency, but rather come from breakthroughs in microarchitecture (Section 3.2.3). We will also consider how to reconcile CPU and GPU designs (Section 3.2.4).

Heterogeneity and multicores are also major obstacles to determining tight worst-case execution times of real-time systems (Section 3.2.5), which we plan to tackle.

Finally, we also describe how we plan to address transversal aspects such reliability (Section 3.2.6), power efficiency (Section 3.2.7), and security (Section 3.2.8).

# 3.2.1. Static Compilation

Static compilation techniques will continue to be relevant to address the characteristics of emerging hardware technologies, such as non-volatile memories, 3D-stacking, or novel communication technologies. These techniques expose new characteristics to the software layers. As an example, non-volatile memories typically have asymmetric read-write latencies (writes are much longer than reads) and different power consumption profiles. PACAP will study the new optimization opportunities and develop tailored compilation techniques for the upcoming compute nodes. New technologies may also be coupled with traditional solutions to offer new trade-offs. We will study how programs can adequately exploit the specific features of the proposed heterogeneous compute nodes.

We propose to build upon iterative compilation [1] to explore how applications perform on different configurations. When possible, Pareto points will be related to application characteristics. The best configuration, however, may actually depend on runtime information, such as input data, dynamic events, or properties that are available only at runtime. Unfortunately a runtime system has little time and means to determine the best configuration. For these reasons, we will also leverage split-compilation [2]: the idea consists in pre-computing alternatives, and embedding in the program enough information to assist and drive a runtime system towards to the best solution.

### 3.2.2. Software Adaptation

More than ever, software will need to adapt to their environment. In most cases, this environment will remain unknown until runtime. This is already the case when one deploys an application to a cloud, or an "app" to mobile devices. The dilemma is the following: for maximum portability, developers should target the most general device; but for performance they would like to exploit the most recent and advanced hardware features. JIT compilers can handle the situation to some extent, but binary deployment requires dynamic binary rewriting. Our work has shown how SIMD instructions can be upgraded from SSE to AVX [3]. Many more opportunities will appear with diverse and heterogeneous processors, featuring various kinds of accelerators.

On shared hardware, the environment is also defined by other applications competing for the same computational resources. It will become increasingly important to adapt to changing runtime conditions, such as the contention of the cache memories, available bandwidth, or hardware faults. Fortunately, optimizing at runtime is also an opportunity, because this is the first time the program is visible as a whole: executable and libraries (including library versions). Optimizers may also rely on dynamic information, such as actual input data, parameter values, etc. We have already developed a software platform [14] to analyze and optimize programs at runtime, and we started working on automatic dynamic parallelization of sequential code, and dynamic specialization.

We started addressing some of these challenges in ongoing projects such as Nano2017 PSAIC Collaborative research program with STMicroelectronics, as well as within the Inria Project Lab MULTICORE. The starting H2020 FET HPC project ANTAREX will also address these challenges from the energy perspective. We will further leverage our platform and initial results to address other adaptation opportunities. Efficient software adaptation will require expertise from all domains tackled by PACAP, and strong interaction between all team members is expected.

<sup>&</sup>lt;sup>2</sup>According to Dennard scaling, as transistors get smaller the power density remains constant, and the consumed power remains proportional to the area.

### 3.2.3. Research directions in uniprocessor microarchitecture

Achieving high single-thread performance remains a major challenge even in the multicore era (Amdahl's law). The members of the PACAP project-team have been conducting research in uniprocessor micro-architecture research for about 20 years covering major topics including caches, instruction front-end, branch prediction, out-of-order core pipeline, branch prediction and value prediction. In particular, in the recent years they have been recognized world leaders in branch prediction [19][9] and in cache prefetching [7] and they have revived the forgotten concept of value prediction [12], [11]. This research was supported by the ERC Advanced grant DAL (2011-2016) and also by Intel. We intend to pursue research on achieving ultimate unicore performance. Below are several non-orthogonal directions that we have identified for midterm research:

- 1. management of the memory hierarchy (particularly the hardware prefetching);

- 2. practical design of very wide issue execution core;

- 3. speculative execution.

#### Memory design issues:

Performance of many applications is highly impacted by the memory hierarchy behavior. The interactions between the different components in the memory hierarchy and the out-of-order execution engine have high impact on performance.

The last *Data Prefetching Contest* held with ISCA 2015 has illustrated that achieving high prefetching efficiency is still a challenge for wide-issue superscalar processors, particularly those featuring a very large instruction window. The large instruction window enables an implicit data prefetcher. The interaction between this implicit hardware prefetcher and the explicit hardware prefetcher is still relatively mysterious as illustrated by Pierre Michaud's BO prefetcher (winner of DPC2) [7]. The first objective of the research is to better understand how the implicit prefetching enabled by the large instruction window interacts with the L2 prefetcher and then to understand how explicit prefetching on the L1 also interacts with the L2 prefetcher.

The second objective of the research is related to the interaction of prefetching and virtual/physical memory. On real hardware, prefetching is stopped by page frontiers. The interaction between TLB prefetching (and on which level) and cache prefetching must be analyzed.

The prefetcher is not the only actor in the hierarchy that must be carefully controlled. Significant benefit can also be achieved through careful management of memory access bandwidth, particularly the management of spatial locality on memory accesses, both for reads and writes. The exploitation of this locality is traditionally handled in the memory controller. However, it could be better handled if larger temporal granularity was available. Finally, we also intend to continue to explore the promising avenue of compressed caches. In particular we recently proposed the skewed compressed cache [15]. It offers new possibility for efficient compression schemes.

### Ultra wide-issue superscalar.

To effectively leverage memory level parallelism, one requires huge out-of-order execution structures as well as very wide issue superscalar processor. For the two past decades, implementing always wider issue superscalar processor has been challenging. The objective of our research on the execution core is to explore (and revisit) directions to allow the design of a very wide-issue (8-to-16 way) out-of-order execution core while mastering its complexity (silicon area, hardware logic complexity, power/energy consumption).

The first direction that we intend to explore is the use of clustered architecture as in our recent work [8]. Symmetric clustered organization allows to benefit from simpler bypass network, but induce large complexity on the issue queue. One remarkable finding of our study [8] is that, when considering two large clusters (e.g. 8-wide) steering large groups of consecutive instructions (e.g.  $64 \mu ops$ ) to the same cluster is quite efficient. This opens opportunities to limit the complexity of the issue queues (monitoring less fewer buses) and register files (reducing number of ports, and number of physical registers) in the clusters, since not all results have to be forwarded to the other cluster.

The second direction that we intend to explore is associated with the approach we developed with Sembrant et al. [16]. It reduces the number of instructions waiting in the instruction queues for the applications benefiting from very large instruction windows. Instructions are dynamically classified as ready (independent from any long latency instruction) or non-ready, and as urgent (part of a dependency chain leading to a long latency instruction) or non-urgent. Non-ready non-urgent instructions can be delayed until the long latency instruction has been executed; this allows to reduce the pressure on the issue queue. This proposition opens the opportunity to consider an asymmetric microarchitecture with a cluster dedicated to the execution of urgent instructions and a second cluster executing the non-urgent instructions. The microarchitecture of this second cluster could be optimized to reduce complexity and power consumption (smaller instruction queue, less aggressive scheduling...)

Speculative execution.

Out-of-order (OoO) execution relies on speculative execution that requires predictions of all sorts: branch, memory dependency, value...

The PACAP members have been major actors of the branch prediction research for the last 20 years; and their proposals have influenced the design of most of the hardware branch predictors in current microprocessors. We will continue to steadily explore new branch predictor designs as for instance [18].

In speculative execution, we have recently revisited value prediction (VP) which was a hot research topic between 1996 and 2002. However it was considered up to recently that value prediction would lead to a huge increase in complexity and power consumption in every stage of the pipeline. Fortunately, we have recently shown that complexity usually introduced by value prediction in the OoO engine can be overcome [12], [11], [19], [9]. First, very high accuracy can be enforced at reasonable cost in coverage and minimal complexity [12]. Thus, both prediction validation and recovery by squashing can be done outside the out-of-order engine, at commit time. Furthermore, we propose a new pipeline organization, EOLE ({Early | Out-of-order | Late}) Execution), that leverages VP with validation at commit to execute many instructions outside the OoO core, in-order [11]. With EOLE, the issue-width in OoO core can be reduced without sacrificing performance, thus benefiting the performance of VP without a significant cost in silicon area and/or energy. In the near future, we will explore new avenues related to value prediction. These directions include register equality prediction and compatibility of value prediction with weak memory models in multiprocessors.

#### 3.2.4. Towards heterogeneous single-ISA CPU-GPU architectures

Heterogeneous single-ISA architectures have been proposed in the literature during the 2000's [56] and are now widely used in the industry (ARM big.LITTLE, NVIDIA 4+1...) as a way to improve power-efficiency in mobile processors. These architectures include multiple cores whose respective microarchitectures offer different trade-offs between performance and energy efficiency, or between latency and throughput, while offering the same interface to software. Dynamic task migration policies leverage the heterogeneity of the platform by using the most suitable core for each application, or even each phase of processing. However, these works only tune cores by changing their complexity. Energy-optimized cores are either identical cores implemented in a low-power process technology, or simplified in-order superscalar cores, which are far from state-of-the-art throughput-oriented architectures such as GPUs.

We propose to investigate the convergence of CPU and GPU at both architecture and compilation levels.

#### Architecture.

The architecture convergence between Single Instruction Multiple Threads (SIMT) GPUs and multicore processors that we have been pursuing [36] opens the way for heterogeneous architectures including latency-optimized superscalar cores and throughput-optimized GPU-style cores, which all share the same instruction set. Using SIMT cores in place of superscalar cores will enable the highest energy efficiency on regular sections of applications. As with existing single-ISA heterogeneous architectures, task migration will not necessitate any software rewrite and will accelerate existing applications.

Compilers for emerging heterogeneous architectures.

Single-ISA CPU+GPU architectures will provide the necessary substrate to enable efficient heterogeneous processing. However, it will also introduce substantial challenges at the software and firmware level. Task placement and migration will require advanced policies that leverage both static information at compile time and dynamic information at run-time. We are tackling the heterogeneous task scheduling problem at the compiler level. As a first step, we are prototyping scheduling algorithms on existing multiple-ISA CPU+GPU architectures like NVIDIA Tegra X1.

### 3.2.5. Real-time systems

Safety-critical systems (e.g. avionics, medical devices, automotive...) have so far used simple unicore hardware systems as a way to control their predictability, in order to meet timing constraints. Still, many critical embedded systems have increasing demand in computing power, and simple unicore processors are not sufficient anymore. General-purpose multicore processors are not suitable for safety-critical real-time systems, because they include complex micro-architectural elements (cache hierarchies, branch, stride and value predictors) meant to improve average-case performance, and for which worst-case performance is difficult to predict. The prerequisite for calculating tight WCET is a deterministic hardware system that avoids dynamic, time-unpredictable calculations at run-time.

Even for multi and manycore systems designed with time-predictability in mind (Kalray MPPA manycore architecture <sup>3</sup>, or the Recore manycore hardware <sup>4</sup>) calculating WCETs is still challenging. The following two challenges will be addressed in the mid-term:

- 1. definition of methods to estimate WCETs tightly on manycores, that smartly analyzes and/or controls shared resources such as buses, NoCs or caches;

- 2. methods to improve the programmability of real-time applications through automatic parallelization and optimizations from model-based designs.

#### 3.2.6. Fault Tolerance

Technology trends suggest that, in tomorrow's computing world, failures will become commonplace due to many factors, and the expected probability of failure will increase with scaling. While well-known approaches, such as error correcting codes, exist to recover from failures and provide fault-free chips, the exponential growth of the number of faults will make them unaffordable in the future. Consequently, other approaches such as fine-grained disabling and reconfiguration of hardware elements (e.g. individual functional units or cache blocks) will become economically necessary. We are going to enter a new era: functionally correct chips with variable performance among chips and throughout their lifetime [58].

Transient and permanent faults may be detected by similar techniques, but correcting them generally involves different approaches. We are primarily interested in permanent faults, even though we do not necessarily disregard transient faults (e.g. the TMR approach in the next paragraph addresses both kind of faults).

#### CPU

Permanent faults can occur anywhere in the processor. The performance implications of faulty cells vary depending on how the array is used in a processor. Most of micro-architectural work aiming at assessing the performance implications of permanently faulty cells relies on simulations with random fault-maps. These studies are, therefore, limited by the fault-maps they use that may not be representative for the average and distributed performance. They also do not consider aging effect.

Considering the memory hierarchy, we have already studied [5] the impact of permanent faults on the average and worst-case performance based on analytical models. We will extend these models to cover other components and other designs, and to analyze the interaction between faulty components.

For identified critical hardware structures, such as the memory hierarchy, we will propose protection mechanisms by for instance using larger cells, or even by selecting a different array organization to mitigate the impact of faults.

<sup>&</sup>lt;sup>3</sup>http://www.kalrayinc.com

<sup>&</sup>lt;sup>4</sup>http://www.recoresystems.com/

Another approach to deal with faults is to introduce redundancy at the code level. We propose to consider static compilation techniques focusing on existing hardware. As an example, we plan to leverage SIMD extensions of current instruction sets to introduce redundancy in scalar code at minimum cost. With these instructions, it will be possible to protect the execution from both soft errors by using TMR (triple modular redundancy) with voters in the code itself, and permanent faults without the need of extra hardware support to deconfigure faulty functional units.

#### Reconfigurable Computing.

In collaboration with the CAIRN project-team, we propose to construct Coarse Grain Reconfigurable Architectures (CGRA) from a sea of basic arithmetic and memory elements organized into clusters and connected through a hierarchical interconnection network. These clusters of basic arithmetic operators (e.g. 8-bit arithmetic and logic units) would be able to be seamlessly configured to various accuracy and data types to adapt the consumed energy to application requirements taking advantage of approximate computations. We propose to add new kinds of error detection (and sometimes correction) directly at the operator level by taking advantage of the massive redundancy of the array. As an example, errors can be tracked and detected in a complex sequence of double floating-point operations by using a reduced-precision version of the same processing.

Such reconfigurable blocks will be driven by compilation techniques, in charge of computing checkpoints, detecting faults, and replaying computations when needed.

Dynamic compilation techniques will help better exploit faulty hardware, by allocating data and computations on correct resources. In case of permanent faults, we will provide a mechanism to reconfigure the hardware, for example by reducing the issue width of VLIW processors implemented in CGRA. Dynamic code generation (JIT compiler) will re-generate code for the new configuration, guaranteeing portability and optimal exploitation of the hardware.

# 3.2.7. Power efficiency

PACAP will address power-efficiency at several levels. First, we will design static and split compilation techniques to contribute to the race for Exascale computing (the general goal is to reach  $10^{18}$  FLOP/s at less than 20 MW). Second, we will focus on high-performance low-power embedded compute nodes. will research new static and dynamic compilation techniques that fully exploit emerging memory and NoC technologies. Finally, in collaboration with the CAIRN project-team, we will investigate the synergy of reconfigurable computing and dynamic code generation.

Green and heterogeneous high-performance computing.

Concerning HPC systems, our approach consists in mapping, runtime managing and autotuning applications for green and heterogeneous High-Performance Computing systems up to the Exascale level. One key innovation of the proposed approach consists of introducing a separation of concerns (where self-adaptivity and energy efficient strategies are specified aside to application functionalities) promoted by the definition of a Domain Specific Language (DSL) inspired by aspect-oriented programming concepts for heterogeneous systems. The new DSL will be introduced for expressing adaptivity/energy/performance strategies and to enforce at runtime application autotuning and resource and power management. The goal is to support the parallelism, scalability and adaptability of a dynamic workload by exploiting the full system capabilities (including energy management) for emerging large-scale and extreme-scale systems, while reducing the Total Cost of Ownership (TCO) for companies and public organizations.

High-performance low-power embedded compute nodes.

We will address the design of next generation energy-efficient high-performance embedded compute nodes. It focuses at the same time on software, architecture and emerging memory and communication technologies in order to synergistically exploit their corresponding features. The approach of the project is organized around three complementary topics: 1) compilation techniques; 2) multicore architectures; 3) emerging memory and communication technologies. PACAP will focus on the compilation aspects, taking as input the software-visible characteristics of the proposed emerging technology, and making the best possible use of the new features (non-volatility, density, endurance, low-power).

#### Hardware Accelerated JIT Compilation.

Reconfigurable hardware offers the opportunity to limit power consumption by dynamically adjusting the number of available resources to the requirements of the running software. In particular, VLIW processors can adjust the number of available issue lanes. Unfortunately, changing the processor width often requires recompiling the application, and VLIW processors are highly dependent of the quality of the compilation, mainly because of the instruction scheduling phase performed by the compiler. Another challenge lies in the high constraints of the embedded system: the energy and execution time overhead due to the JIT compilation must be carefully kept under control.

We started exploring ways to reduce the cost of JIT compilation targeting VLIW-based heterogeneous many-core systems. Our approach lies on a hardware/software JIT compiler framework. While basic optimizations and JIT management are performed in software, the compilation back-end is implemented by means of specialized hardware. This back-end involves both instruction scheduling and register allocation, which are known to be the most time-consuming stages of such a compiler.

# 3.2.8. Security

Security is a mandatory concern of any modern computing system. Various threat models have led to a multitude of protection solutions. ALF already has contributions, thanks to the HAVEGE [62] random number generator, and code obfuscating techniques (the obfuscating just-in-time compiler [55], or thread-based control flow mangling [60]).

We plan to partner with security experts who can provide intuition, know-how and expertise, in particular in defining threat models, and assessing the quality of the solutions. Our background in compilation and architecture will help design more efficient and less expensive protection mechanisms.

We already have ongoing research directions related to security. We also plan to partner with the Inria/CentraleSupelec CIDRE project-team to design a tainting technique based on a just-in-time compiler.

#### Compiler-based data protection.

We will specify and design error correction codes suitable for an efficient protection of sensitive information in the context of Internet of Things (IoT) and connected objects. We will partner with experts in security and codes to prototype a platform that demonstrates resilient software. PACAP's expertise will be key to select and tune the protection mechanisms developed within the project, and to propose safe, yet cost-effective solutions from an implementation point of view.

#### JIT-based tainting.

Dynamic information flow control (DIFC, also known as *tainting*) is used used to detect intrusions and to identify vulnerabilities. It consists in attaching metadata (called *taints* or *labels*) to information containers, and to propagate the taints when particular operations are applied to the containers: reads, writes, etc. The goal is then to guarantee that confidential information is never used to generate data sent to an untrusted container; conversely, data produced by untrusted entities cannot be used to update sensitive data.

The containers can be of various granularities: fine-grain approaches can deal with single variables, coarser-grain approaches consider a file as a whole. The CIDRE project-team has developed several DIFC monitors. kBlare is coarse-grain monitor in the Linux kernel. JBlare is a fine-grain monitor for Java applications. Fine-grain monitors provide a better precision at the cost of a significant overhead in execution time.

We propose to combine the expertise of CIDRE in DIFC with our expertise in JIT compilation to design hybrid approaches. An initial static analysis of the program prior to installation or execution will feed information to a dynamic analyzer that propagates taints during just-in-time compilation.

# 4. Application Domains

# 4.1. Any computer usage

The PACAP team is working on the fundamental technologies for computer science: processor architecture, performance-oriented compilation and guaranteed response time for real-time. The research results may have impacts on any application domain that requires high performance execution (telecommunication, multimedia, biology, health, engineering, environment...), but also on many embedded applications that exhibit other constraints such as power consumption, code size and guaranteed response time. Our research activity implies the development of software prototypes.

# 5. Highlights of the Year

# 5.1. Highlights of the Year

André Seznec was elevated as an ACM Fellow in December 2016 with the citation: "For contributions to branch prediction and cache memory design".

André Seznec won the three tracks of the 5th Championship on Branch Prediction.

#### 5.1.1. Awards

Sajith Kalathingal, Sylvain Collange, Bharath Swamy and André Seznec received the Best Paper award of the SBAC-PAD 2016 conference.

Damien Hardy, Isabelle Puaut, Yiannakis Sazeides won the best paper award of the Embedded Systems Software track at DATE 2016: Probabilistic WCET estimation in presence of hardware for mitigating the impact of permanent faults. Design, Automation and Test in Europe. Dresden, Germany, March 2016.

Aswinkumar Sridharan and André Seznec won the best paper award for "Discrete Cache Insertion Policies for Shared Last Level Cache Management on Large Multicores" at the 30th IEEE International Parallel & Distributed Processing Symposium, May 2016, Chicago.

For his PhD thesis [10] "Increasing the Performance of Superscalar Processors through Value Prediction", Arthur Perais received:

- Prix de thèse Fondation Rennes 1, 1er Prix de l'école doctorale MATISSE;

- Prix de thèse Gilles Kahn, accessit.

#### BEST PAPERS AWARDS:

[46]

A. SEZNEC. *TAGE-SC-L Branch Predictors Again*, in "5th JILP Workshop on Computer Architecture Competitions (JWAC-5): Championship Branch Prediction (CBP-5)", Seoul, South Korea, June 2016, https://hal.inria.fr/hal-01354253

[45]

A. SEZNEC. *Exploring branch predictability limits with the MTAGE+SC predictor* \*, in "5th JILP Workshop on Computer Architecture Competitions (JWAC-5): Championship Branch Prediction (CBP-5)", Seoul, South Korea, June 2016, 4 p. , https://hal.inria.fr/hal-01354251

[36]

S. KALATHINGAL, S. COLLANGE, B. NARASIMHA SWAMY, A. SEZNEC. *Dynamic Inter-Thread Vectorization Architecture: extracting DLP from TLP*, in "International Symposium on Computer Architecture and High-Performance Computing (SBAC-PAD)", Los Angeles, United States, October 2016, <a href="https://hal.inria.fr/hal-01356202">https://hal.inria.fr/hal-01356202</a>

[35]

D. HARDY, I. PUAUT, Y. SAZEIDES. *Probabilistic WCET estimation in presence of hardware for mitigating the impact of permanent faults*, in "Design, Automation and Test in Europe", Dresden, Germany, March 2016, https://hal.inria.fr/hal-01259493

[48]

A. SRIDHARAN, A. SEZNEC. Discrete Cache Insertion Policies for Shared Last Level Cache Management on Large Multicores, in "30th IEEE International Parallel & Distributed Processing Symposium", Chicago, United States, May 2016, https://hal.inria.fr/hal-01259626

# 6. New Software and Platforms

# 6.1. ATMI

KEYWORDS: Analytic model - Chip design - Temperature

SCIENTIFIC DESCRIPTION

Research on temperature-aware computer architecture requires a chip temperature model. General purpose models based on classical numerical methods like finite differences or finite elements are not appropriate for such research, because they are generally too slow for modeling the time-varying thermal behavior of a processing chip.

We have developed an ad hoc temperature model, ATMI (Analytical model of Temperature in MIcroprocessors), for studying thermal behaviors over a time scale ranging from microseconds to several minutes. ATMI is based on an explicit solution to the heat equation and on the principle of superposition. ATMI can model any power density map that can be described as a superposition of rectangle sources, which is appropriate for modeling the microarchitectural units of a microprocessor.

FUNCTIONAL DESCRIPTION

ATMI is a library for modelling steady-state and time-varying temperature in microprocessors. ATMI uses a simplified representation of microprocessor packaging.

Participant: Pierre MichaudContact: Pierre Michaud

• URL: https://team.inria.fr/pacap/software/atmi/

# 6.2. Heptane

KEYWORDS: Static analysis - Real time - Performance - WCET - IPET - Worst Case Execution Time SCIENTIFIC DESCRIPTION

WCET estimation

Status: Registered with APP (Agence de Protection des Programmes). Available under GNU General Public License v3, with number IDDN.FR.001.510039.000.S.P.2003.000.10600.

The aim of Heptane is to produce upper bounds of the execution times of applications. It is targeted at applications with hard real-time requirements (automotive, railway, aerospace domains). Heptane computes WCETs using static analysis at the binary code level. It includes static analyses of microarchitectural elements such as caches and cache hierarchies.

For more information, please contact Damien Hardy or Isabelle Puaut.

FUNCTIONAL DESCRIPTION

In a hard real-time system, it is essential to comply with timing constraints, and Worst Case Execution Time (WCET) in particular. Timing analysis is performed at two levels: analysis of the WCET for each task in isolation taking account of the hardware architecture, and schedulability analysis of all the tasks in the system. Heptane is a static WCET analyser designed to address the first issue.

Participants: Isabelle Puaut, Damien Hardy, Loïc Besnard

Partner: Université de Rennes 1

Contact: Isabelle Puaut

• URL: https://team.inria.fr/pacap/software/heptane/

# 6.3. Tiptop

KEYWORDS: HPC - Performance - CPU - Cache - Cycles - Instructions - Branch predictor SCIENTIFIC DESCRIPTION

Tiptop is written in C. It can take advantage of librourses when available for pseudo-graphic display.

Performance, hardware counters, analysis tool.

Status: Registered with APP (Agence de Protection des Programmes). Available under GNU General Public License v2, with number IDDN.FR.001.450006.000.S.P.2011.000.10800. Current version is 2.3, released July 2015.

Tiptop has been integrated in major Linux distributions, such as Fedora, Debian, Ubuntu.

Tiptop is a new simple and flexible user-level tool that collects hardware counter data on Linux platforms (version 2.6.31+). The goal is to make the collection of performance and bottleneck data as simple as possible, including simple installation and usage. In particular, we stress the following points.

Installation is only a matter of compiling the source code. No patching of the Linux kernel is needed, and no special-purpose module needs to be loaded.

No privilege is required, any user can run tiptop

FUNCTIONAL DESCRIPTION

Today's microprocessors have become extremely complex. To better understand the multitude of internal events, manufacturers have integrated many monitoring counters. Tiptop can be used to collect and display the values from these performance counters very easily. Tiptop may be of interest to anyone who wants to optimise the performance of their HPC applications.

Participant: Erven RohouContact: Erven Rohou

• URL: http://tiptop.gforge.inria.fr

# 6.4. ATC

Address Trace Compression

KEYWORDS: Compressing - Decompressing - Address traces

FUNCTIONAL DESCRIPTION

ATC is a utility and a C library for compressing/decompressing address traces. It implements a new lossless transformation, Bytesort, that exploits spatial locality in address traces. ATC leverages existing general-purpose compressors such as gzip and bzip2. ATC also provides a lossy compression mode that yields higher compression ratios while preserving certain important characteristics of the original trace.

Participant: Pierre MichaudContact: Pierre Michaud

• URL: https://team.inria.fr/pacap/software/atc/

### 6.5. Barra

Modelisation of a GPU architecture

KEYWORDS: Simulator - GPU - Computer architecture

SCIENTIFIC DESCRIPTION

Research on throughput-oriented architectures demands accurate and representative models of GPU architectures in order to be able to evaluate new architectural ideas, explore design spaces and characterize applications. The Barra project is a simulator of the NVIDIA Tesla GPU architecture.

Barra builds upon knowledge acquired through micro-benchmarking, in order to provide a baseline model representative of industry practice. The simulator provides detailed statistics to identify optimization opportunities and is fully customizable to experiment ideas of architectural modifications. Barra incorporates both a functional model and a cycle-level performance model.

FUNCTIONAL DESCRIPTION

Barra simulates CUDA programs at the assembly language level (Tesla ISA). Its ultimate goal is to provide a 100 % bit-accurate simulation, offering bug-for-bug compatibility with NVIDIA G80-based GPUs. It works directly with CUDA executables, neither source modification nor recompilation is required.

Barra is primarily intended as a tool for research in computer architecture, although it can also be used to debug, profile and optimize CUDA programs at the lowest level.

• Participants: Sylvain Collange, David Defour, Alexandre Kouyoumdjian and Fabrice Mouhartem

• Contact: Sylvain Collange

URL: http://barra.gforge.inria.fr/

# **6.6. If-memo**

KEYWORD: Performance, function memoization, dynamic optimization

**Status:** Ongoing development, early prototype. Registered with APP (Agence de Protection des Programmes) under number IDDN.FR.001.250013.000.S.P.2015.000.10800.

SCIENTIFIC DESCRIPTION

Memoization is the technique of saving result of executions so that future executions can be omitted when the inputs repeat. Memoization has been proposed in previous literature at the instruction level, basic block level and function level using hardware as well as pure software level approaches including changes to programming language.

We proposed software memoization of pure functions for procedural languages. We rely on the operating system loader, taking advantage of the LD\_PRELOAD feature of UNIX systems. By setting this variable to the path of a shared library, we instruct the loader to first look to missing symbols in that library. Our library redefines the functions we wish to intercept. The interception code is very straightforward: it receives the same parameter as the target function and checks in a table (a software cache) if this value is readily available. In the favorable case, the result value is immediately returned. Otherwise, we invoke the original function, and store the result in the cache before returning it.

Our technique does not require the availability of source code and thus can be applied even to commercial applications as well as applications with legacy codes. As far as users are concerned, enabling memoization is as simple as setting an environment variable. We validated If-memo with x86-64 platform using both GCC and icc compiler tool-chains, and ARM cortex-A9 platform using GCC.

Participants: Erven Rohou and Arjun Suresh

Contact: Erven Rohou

#### 6.7. Padrone

KEYWORDS: Legacy code - Optimization - Performance analysis - Dynamic Optimization

**Status:** Registered with APP (Agence de Protection des Programmes) under number IDDN.FR.001.250013. 000.S.P.2015.000.10800.

FUNCTIONAL DESCRIPTION

Padrone is new platform for dynamic binary analysis and optimization. It provides an API to help clients design and develop analysis and optimization tools for binary executables. Padrone attaches to running applications, only needing the executable binary in memory. No source code or debug information is needed. No application restart is needed either. This is especially interesting for legacy or commercial applications, but also in the context of cloud deployment, where actual hardware is unknown, and other applications competing for hardware resources can vary. The profiling overhead is minimum.

Participants: Erven Rohou and Emmanuel Riou

Contact: Erven Rohou

https://team.inria.fr/pacap/software/Padrone/

# 6.8. STiMuL

Steady temperature in Multi-Layers components

FUNCTIONAL DESCRIPTION