Section: Partnerships and Cooperations

National Initiatives

Insa-Spie IoT Chair

The Insa-Spie IoT Chair http://www.citi-lab.fr/chairs/iot-chair/ relies on the expertise of the CITI Lab. The skills developed within the different teams of the lab integrate the study, modelling, conception and evaluation of technologies for communicating objects and dedicated network architectures. It deals with network, telecom and software matters as well as societal issues such as privacy. The chair will also lean on the skills developed at INSA Lyon or in IMU LabEx.

Inria Project Lab: ZEP

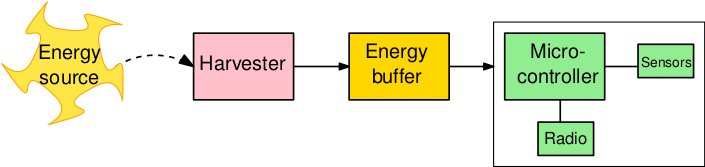

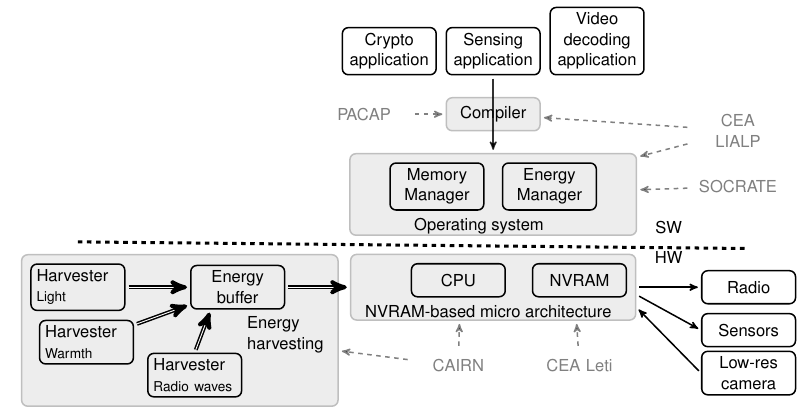

The ZEP project addresses the issue of designing tiny computing objects with no battery by combining non-volatile memory (NVRAM), energy harvesting, micro-architecture innovations, compiler optimizations, and static analysis. The main application target is Internet of Things (IoT) where small communicating objects will be composed of this computing part associated to a low-power wake-up radio system. The ZEP project gathers four Inria teams that have a scientific background in architecture, compilation, operating system and low power together with the CEA Lialp and Lisan laboratories of CEA LETI & LIST. The major outcomes of the project will be a prototype harvesting board including NVRAM and the design of a new microprocessor associated with its optimizing compiler and operating system.

|

The scientific work (in progress) is organized around three fields :

-

dedicated compiler pass that computes a worst-case energy consumption

-

operating system managing NVRAM and energy, ensuring memory consistency across power outages

The project is illustrated by the figure 5, where PACAP, SOCRATE, CORSE, and CAIRN are the teams involved in the project.

Another important goal of the project is to structure the research and innovation that should occur within Inria to prepare the important technological shift brought by NVRAM technologies.

ANR - Imprenum

The objective of this project (INSA-Lyon, École Normale Supérieure de Lyon, CEA LETI) is to promote accuracy as a first class concern in all the levels of a computing system:

-

at the hardware level, with better support for lower-than-standard and higher-than-standard precisions;

-

at the level of run-time support software, in particular answering the memory management challenges entailed by adaptive precision;

-

at the lower level of mathematical libraries (kernel level), for instance BLAS for linear algebra, enhancing well established libraries with precision and accuracy control;

-

at the higher level of mathematical libraries (solver level, including algebraic linear solvers such as LAPACK, ad hoc steppers for Ordinary Differential Equation, eigenvalues kernels, triangularization problems for computational geometry, etc.) Here, accuracy and precision control of the lower levels should enable higher-level properties such as convergence and stability;

-

at the compiler level, enhancing optimising compilers with novel optimisations related to precision and accuracy;

-

at the language level, embedding accuracy specification and control in existing languages, and possibly defining domain-specific languages with accuracy-aware semantics for some classes of applications.

ADT SytaRiot

The Riot system (https://www.riot-os.org/) is well known within Inria, it is a joint implementation of Inria and Freie Universität Berlin which is today one of the most widely used open-source OS on small embedded systems. The arrival of non-volatile memories promises a new generation of sensors on which the memory hierarchy will be more heterogeneous than today. The communicating system will be able to undergo a power cut em complete and resume its current activity when power returns.

Sytare (https://gitlab.inria.fr/citi-lab/sytare/), developed for three years by the Socrates team (with the support of an ADT), targets intermittent feeding which will arrive when the technologies of harvesting (recovery of ambient energy) are democratized.

The objective of this ADT is to make Riot compatible with NVRAM-based architecture, therefore to integrate Sytare with Riot and thus open Riot to ultra low power platforms containing NVRAM, eg Texas microcontrollers Instrument MSP430FR5969.

Digital Hardware AI Architectures

Florent de Dinechin participates to the chair Digital Hardware AI Architectures held by Prof. Frédéric Pétrot at the Multidisciplinary Institute in Artificial Intelligence (MIAI) of Grenoble. The other participants are François Duhem (Spintec/CEA) and Fabrice Rastello (LIG/Inria), with industrial partners Google France, Kalray, STMicroelectronics, and Upmem.

This chair funds the PhD of Maxime Christ, which studies how very low-precision arithmetic formats may improve the efficiency of the learning phase of neural networks.