Section: Scientific Foundations

Introduction

Embedded systems are not new, but their pervasive introduction in ordinary-life objects (cars, telephone, home appliances) brought a new focus onto design methods for such systems. New development techniques are needed to meet the challenges of productivity in a competitive environment. Synchronous languages rely on the synchronous hypothesis, which lets computations and behaviors be divided into a discrete sequence of computation steps which are equivalently called reactions or execution instants. In itself this assumption is rather common in practical embedded system design.

But the synchronous hypothesis adds to this the fact that, inside each instant, the behavioral propagation is well-behaved (causal), so that the status of every signal or variable is established and defined prior to being tested or used. This criterion, which may be seen at first as an isolated technical requirement, is in fact the key point of the approach. It ensures strong semantic soundness by allowing universally recognized mathematical models to be used as supporting foundations. In turn, these models give access to a large corpus of efficient optimization, compilation, and formal verification techniques. The synchronous hypothesis also guarantees full equivalence between various levels of representation, thereby avoiding altogether the pitfalls of non-synthesizability of other similar formalisms. In that sense the synchronous hypothesis is, in our view, a major contribution to the goal of model-based design of embedded systems.

We shall describe the synchronous hypothesis and its mathematical background, together with a range of design techniques enpowered by the approach. Declarative formalisms implementing the synchronous hypothesis can be cast into a model of computation [11] consisting of a domain of traces or behaviors and of semi-lattice structure that renders the synchronous hypothesis using a timing equivalence relation: clock equivalence. Asynchrony can be superimposed on this model by considering a flow equivalence relation as well as heterogeneous systems [33] by parameterizing composition with arbitrary timing relations.

A synchronous model of computation

We consider a partially-ordered set of tags to denote instants seen as symbolic periods in time during which a reaction takes place. The relation says that occurs before . Its minimum is noted 0. A totally ordered set of tags is called a chain and denotes the sampling of a possibly continuous or dense signal over a countable series of causally related tags. Events, signals, behaviors and processes are defined as follows:

-

an event is a pair consisting of a value and a tag ,

-

a signal is a function from a chain of tags to a set of values,

-

a behavior is a function from a set of names to signals,

-

a process is a set of behaviors that have the same domain.

In the remainder, we write for the tags of a signal , for the domain of , for the projection of a behavior on a set of names and for its complementary.

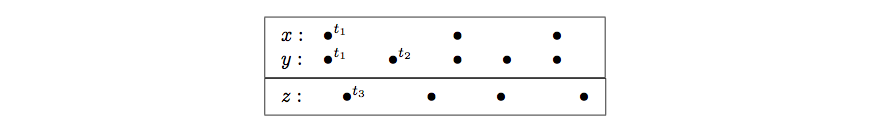

Figure 1 depicts a behavior over three signals named , and . Two frames depict timing domains formalized by chains of tags. Signals and belong to the same timing domain: is a down-sampling of . Its events are synchronous to odd occurrences of events along and share the same tags, e.g. . Even tags of , e.g. , are ordered along its chain, e.g. , but absent from . Signal belongs to a different timing domain. Its tags are not ordered with respect to the chain of .

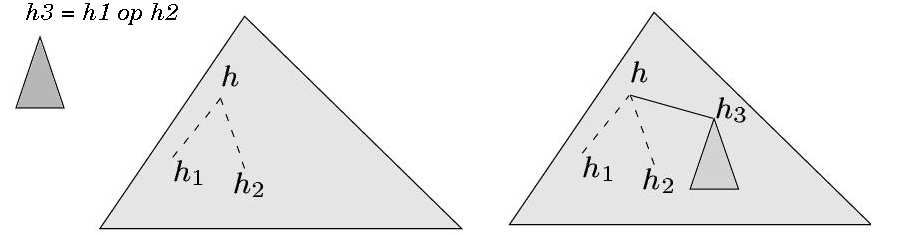

Composition

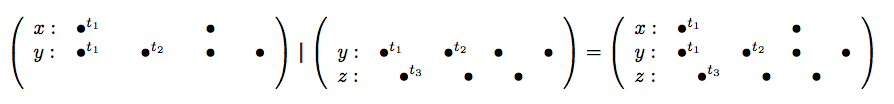

Synchronous composition is noted and defined by the union of all behaviors (from ) and (from ) which hold the same values at the same tags for all signal they share. Figure 2 depicts the synchronous composition (Figure 2 , right) of the behaviors (Figure 2 , left) and the behavior (Figure 2 , middle). The signal , shared by and , carries the same tags and the same values in both and . Hence, defines the synchronous composition of and .

Scheduling

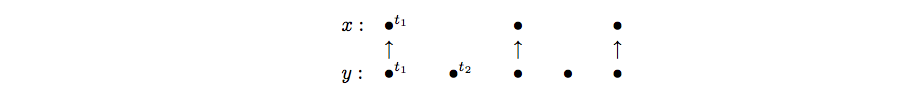

A scheduling structure is defined to schedule the occurrence of events along signals during an instant . A scheduling is a pre-order relation between dates where represents the time and the location of the event. Figure 3 depicts such a relation superimposed to the signals and of Figure 1 . The relation , for instance, requires to be calculated before at the instant . Naturally, scheduling is contained in time: if then for any and and if then .

Structure

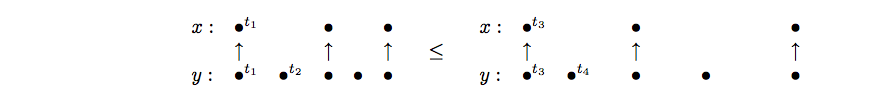

A synchronous structure is defined by a semi-lattice structure to denote behaviors that have the same timing structure. The intuition behind this relation is depicted in Figure 4 . It is to consider a signal as an elastic with ordered marks on it (tags). If the elastic is stretched, marks remain in the same relative (partial) order but have more space (time) between each other. The same holds for a set of elastics: a behavior. If elastics are equally stretched, the order between marks is unchanged.

In Figure 4 , the time scale of and changes but the partial timing and scheduling relations are preserved. Stretching is a partial-order relation which defines clock equivalence. Formally, a behavior is a stretching of of same domain, written , iff there exists an increasing bijection on tags that preserves the timing and scheduling relations. If so, is the image of by . Last, the behaviors and are said clock-equivalent, written , iff there exists a behavior s.t. and .

A declarative design language

Signal [6] is a declarative design language expressed within the polychronous model of computation. In Signal, a process is an infinite loop that consists of the synchronous composition of simultaneous equations over signals named . The restriction of a signal name to a process is noted .

Equations in Signal more generally denote processes that define timing relations between input and output signals. There are four primitive combinators in Signal:

-

delay , initially defines the signal by the value and then by the previous value of the signal . The signal and its delayed copy are synchronous: they share the same set of tags . Initially, at , the signal takes the declared value and then, at tag , the value of at tag .

-

sampling , defines by when is true (and both and are present); is present with the value at only if is present with at and if is present at with the value true. When this is the case, one needs to schedule the calculation of and before , as depicted by .

-

merge , defines by when is present and by otherwise. If is absent and present with at then holds . If is present (at or ) then holds its value whether is present (at ) or not (at ).

The structuring element of a Signal specification is a process. A process accepts input signals originating from possibly different clock domains to produce output signals when needed. This allows, for instance, to specify a counter where the inputs tick and reset and the output value have independent clocks. The body of counter consists of one equation that defines the output signal value . Upon the event reset , it sets the count to 0. Otherwise, upon a tick event, it increments the count by referring to the previous value of value and adding 1 to it. Otherwise, if the count is solicited in the context of the counter process (meaning that its clock is active), the counter just returns the previous count without having to obtain a value from the tick and reset signals.

process counter = (? event tick, reset ! integer value)

(| value := (0 when reset)

default ((value$ init 0 + 1) when tick)

default (value$ init 0)

|);

A Signal process is a structuring element akin to a hierarchical block diagram. A process may structurally contain sub-processes. A process is a generic structuring element that can be specialized to the timing context of its call. For instance, the definition of a synchronized counter starting from the previous specification consists of its refinement with synchronization. The input tick and reset clocks expected by the process counter are sampled from the boolean input signals tick and reset by using the when tick and when reset †expressions. The count is then synchronized to the inputs by the equation reset ^= tick ^= count .

process synccounter = (? boolean tick, reset ! integer value)

(| value := counter (when tick, when reset)

| reset ^= tick ^= value

|);

Compilation of Signal

Sequential code generation starting from a Signal specification starts with an analysis of its implicit synchronization and scheduling relations. This analysis yields the control and data flow graphs that define the class of sequentially executable specifications and allow to generate code.

Synchronization and scheduling specifications

In Signal, the clock of a signal denotes the set of instants at which the signal is present. It is represented by a signal that is true when is present and that is absent otherwise. Clock expressions represent control. The clock (resp. ) represents the time tags at which a boolean signal is present and true (resp. false).

The empty clock is written 0 and clock expressions combined using conjunction, disjunction and symmetric difference. Clock equations are Signal processes: the equation synchronizes the clocks and while specifies the containment of in . Explicit scheduling relations allow to schedule the calculation of signals (e.g. after at the clock ).

Synchronization and scheduling analysis

A Signal process corresponds to a system of clock and scheduling relations that denotes its timing structure. It can be defined by induction on the structure of using the inference system of Figure 5 .

x := y$ init v : ^x ^= ^y

x := y when z : ^x ^= ^y when z | y -> x when z

x := y default z : ^x ^= ^y default ^z | y -> x when ^y | z -> x when ^z ^- ^y

Hierarchization

The clock and scheduling relations of a process define the control-flow and data-flow graphs that hold all necessary information to compile a Signal specification upon satisfaction of the property of endochrony. A process is said endochronous iff, given a set of input signals and flow-equivalent input behaviors, it has the capability to reconstruct a unique synchronous behavior up to clock-equivalence: the input and output signals are ordered in clock-equivalent ways.